Sposób i układ szybkiego równoległego przetwarzania sygnałó · PDF...

Transcript of Sposób i układ szybkiego równoległego przetwarzania sygnałó · PDF...

Charakterystyka wynalazkuPrzedmiotem wynalazku jest sposób i układ do szybkiego równoległego przetwarzania sygnałów wielowy-miarowych.

W większości znanych rozwiązań przekształceń sygnałów jedno i wielowymiarowych, obliczenia współczyn-ników przekształcenia wykonywane są dopiero po wprowadzeniu wszystkich danych wejściowych. Równo-ległość obliczeń opiera się na wykorzystaniu grup procesorów czy dzielenia danych na bloki co spowalnia szybkość obliczeń i wymaga złożonych i często nieekonomicznych zasobów sprzętowych. Nie znaleziono jeszcze rozwiązań, gdzie w odpowiednio zorganizowanej pamięci umieszczone zostały obliczone części przekształcenia, które są następnie odpowiednio sumowane.

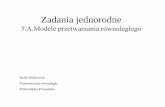

W proponowanym sposobie do szybkiego równoległego przetwarzania sygnałów, wejściowy M·…·N wymia-rowy sygnał {xm,...,n} o zadanej bitowości zamieniany jest na podstawie skanowania na sygnał jednowymia-rowy i przesyłany jest szeregowo w postaci wartości próbek na wejście układu formującego adresy komórek

pamięci. w celu zwiększenia szybkości obliczeń przekształcenia klasy χp,...,q = αp...αq xm,...,n f(m,..., n, p,..., q),

gdzie: χp,...,q - wynik przekształcenia sygnału wielowymiarowego dla współczynnika o indeksach p,...,q, αp... αq - współczynniki skalujące, xm,...,n - wartość sygnału wejściowego o indeksach m,...,n, f(m,..., n, p,..., q), - funkcja transformująca, M·…·N - rozmiar sygnału wejściowego oraz wyjściowego, wartości próbek wraz z ich numerami tworzą adresy odpowiednich komórek pamięci, z których to komórek równolegle odczyty-wane są iloczyny próbek i odpowiednich składowych funkcji transformacji oraz współczynników skalujących {xm, n · f(m, n, p, q)·αp·αq}. Następnie iloczyny te są sumowane i akumulowane w każdym kanale oddziel-nie. Do obliczeń wykorzystuje się równoległe przetwarzanie sygnału w M·…·N kanałach formujących taką samą ilość składowych sygnału wyjściowego, w rezultacie czego po M·…·N taktach formowany jest sygnał wyjściowy. W tym sposobie, każdy kanał reprezentuje odpowiednią składową sygnału wejściowego tego przetwarzania. Układ do szybkiego równoległego przetwarzania sygnałów M·…·N wymiarowych zawiera-jący M·…·N pamięci /2.1 … 2. M·…·N/, M·…·N sumatorów-akumulujących /3.1 … 3. M·…·N/ oraz układ sterowania /4/, sygnał wejściowy o bitowości b oraz sygnał zegarowy CLK podawane są na transkoder /1/, który formuje adresy komórek pamięci o bitowościach c. Adresy te jednocześnie podawane są na odpo-wiednie wejścia adresowe A wszystkich M·…·N pamięci /2.1 … 2. M·…·N/. Wyjście każdej pamięci /2.1 … 2. M·…·N/ jest połączone z wejściem sygnałowym odpowiedniego sumatora-akumulującego /3.1 … 3. M·…·N/ za pomocą szyny o bitowości d. Wyjściowe sygnały sumatorów-akumulujących /3.1 … 3. M·…·N/ o bitowości

VERTE

Sposób i układ szybkiego równoległegoprzetwarzania sygnałów

TWÓRCY: prof. dr hab. inż. Włodzimierz Pogribny, dr inż. Marcin Drechny

WYDZIAŁ TELEKOMUNIKACJI, INFORMATYKI I ELEKTROTECHNIKIal. Prof. S. Kaliskiego 7, 85-796 Bydgoszcztel. +(48 52) 340-85-63, 340-80-08ZAKŁAD ELEKTROENERGETYKI

e, gdzie e≥d, wyznaczają kolejne współczyn-niki przetwarzania we wszystkich kanałach. Wejściowy sygnał zegarowy CLK przesyłany jest także na wejście układu sterowania /4/. Układ sterowania /4/ posiada trzy wyjścia z których pierwsze (Read) jest połączone równolegle z wejściem RD wszystkich M·…·N pamięci /2.1 … 2. M·…·N/. Sygnał RD steruje odczytem z pamięci. Drugie wyjście układu sterującego /4/ (Add) połączone jest rów-nolegle z wejściami Add układów sumująco--akumulujących /3.1 … 3. M·…·N/ wszystkich kanałów. Trzecie wyjście układu sterowania /4/ Reset, jest połączone z odpowiednim wejściem układów sumująco-akumulują-cych /3.1 … 3. M·…·N/ i służy do kasowania zawartości sumatorów-akumulujących /3.1 … 3. M·…·N/ po ich odczycie.

Zastosowanie w praktyceUkład może zostać wykonany jako specjalizowany układ do równoległego szybkiego obliczania różnych typów przekształceń sygnałów M·…·N wymiarowych.

Potencjalni odbiorcySposób według wynalazku umożliwia różne aplikacje układowe jak i programowe w szczególności umoż-liwia realizację przedstawionego sposobu na szybkich, wydajnych, tanich a także umożliwiających pracę w czasie rzeczywistym, układach pól programowalnych takich jak np. FPGA.

Sposób i układ szybkiego równoległegoprzetwarzania sygnałów

KONTYNUACJA ZE STRONY 1.

Projekt Współfinansowany ze środków Unii Europejskiej w ramach Europejskiego Funduszu Rozwoju Regionalnego

Bezpłatny materiał informacyjny

ul. Ks. A. Kordeckiego 20, 85-789 Bydgoszcz | wspolpraca.utp.edu.pl

Układ szybkiego równoległego przetwarzania sygnałów.