Logica Digital Tema2

-

Upload

leofrancoquique -

Category

Documents

-

view

58 -

download

9

description

Transcript of Logica Digital Tema2

-

1

'""""

1' -..,

r-1

J

') ~

1 ~

1 --".

PEDRO VALVERDE 1111 G O

AUtOR: PEDRO VAL VE.:::tDE MONTERO DE?ARTAMENTO DE ELECTRONICA DEL "lES" MIGUEL DE CeRVANTES" . MURC~A C:Ct.O ::.:)RMA TIVO DE GRADO SUPE:::tlOR: DESARROLLO DE PRODUCTOS E:L:::CIRNICQS. AO: 2003-2004

-

/

CONTENIDOS DE LA UNIDAD TEMATICA

. ----'

INTRODUCC~ON A LOS SlSTFMAS COMBINAC;ONALES. .- - ~ . ~-~; _..._

COD!F~CADORES. coogFJCADORES DE PRiORiDAD .REPRESENTAC;N {~ DE FUNC~ONES. EL 74148.

- DECODIF!CADORES. DECODiFiCADOR DE 7 SEGMENTOS 7447. OTROS DECOFDIFiCADORES~ REPRESENTAC2N DE fUNC~ONES.

- MULT~PLEXORES. ESTUDIO. DEL 74151. IMPLEMENTACiON DE FUNCIONES LGaCAS. APL!CACIONES.

- AN.i.JS~S DE DECODIFiCADOR-DEMUL T~PLEXOR. ESTUDaO DEL 7 442. OTRAS APL!CAC~ON!ES DE INTERES.

- ANL3SS DE COMPARADOR~S. ESTUD!O DEL C!RCUITO 7485. CONBOONES SiER~!E Y PARALELO.

- C~CUDTOS MA TEili1 TBCOS. SUMA Y RESTA EN BiNAiR30. SE;l;1~SUfu1ADOR -Y SUMADOR COMPL~TO~ SUMADORES BNAR~OS DE V AR~OS B~TS. SUMADOR-RESTADOR DE S~GNO Y MAGNITUD. SUMADOR-RESTADOR ~ BCD. ESTUDIO DE CJ. SUMADORES DE DOS Y CUATRO EB"TS. ~

- ANlJS~S DE LA UN~OAD ARUTM~ a HCO LG~CA. ESTUDiO DEL CJ!RCUTO . ~ , ~

ANAL~s;s 74181.

- COLECC~N DE PRCT~CAS Y EJERClC;os PROPUESTOS DE LOS TEMAS TRATADOS ANTERDORMENTE.

.

:~~;.~ . ...

. .

. ,-..

-

,.

A

., ---".

l

. ) _

.-l. _ _!._ .

.):~. ,

Circuiros Comhinacivna!es MSJ 1

TElVIA2. SISTElVJAS COlVIBINACIONALES MSI.

INTRODUCCIN Los sistemas combinacionales son aquellos en los que las salidas dependen

exclusivamente de las entradas, luego para una r:tjsma entrada siempre se tiene la misma salida.

Hasta ahora el diseo de funciones lgicas, o de circuitos lgicos, se ha reaiizado mediante el uso exclusivo .. de puertas bsicas. Los circuitos que contienen estas puertas bsicas son conocidos como SSI (Small Scale of Integration) por que contienen un nmero pequeo de transistores . El diseo que se realiza con estos dispositivos se denomina CUSTOIVI.

Un paso ms profundo en el diseo HARDW ~ es realizar un diseo SEMJ-CUSTOIYI, basado ei1 el uso de bloques constructores. ms complejos. Esto se puede hecer mediante el uso de sistemas o circuitos lYISI (Medium Scale of Integration) dnde el nmero de puertas bsicas puede llegar a 1 OO.

Ms avanzados son los sistemas LSI (Large S ca] e ofintegration ~ 1 000), VLSI (Ver Large Scale of Integration >1000), y ULSI (Ultra Large Scale of Integration > 1 00000).

En un computador se realizan principalmente operaciones de codificacin y decodificacin de datos usando codificadores y decodificadores; transmisin y control de datosusando lneas de bus, multiplexadores y demultplexadores ; y procesado de datos mediante circuitera aritmtica.

En nuestro computador podemos encontrarnos los siguientes sistemas MSI:

CODIFICWORES Y DECODIFICADORES IvfULTIPLEXORES Y DEiviULTIPLEXORES ,. SUiviADORES, C011PARADORES ...

Adems estos dispositivos pueden usarse tambin para la realizacin de funciones complejas con un considerable ahorro de rea frente al uso de puertas bsicas (circuitos SSI) .

:'

-

Circuitos Comhinu.drmales MSJ :2

DECODIFICADORES

Un decodificador es un circuito lgico con n entradas y 2n salidas, tal que para cada combinacin de entradas se activa al menos una salida. Si slo se activa una salida se denomina decoditicador completo..

Por ejemplo este es un circuito decodificador completo de 3 a 8 lneas , permitira la activacin de un dispositivo al proporcionarle la direccin de dicho dispositivo. Dispone de una entrada de HABILITACIN (enable) que conecta o desconecta el dispositivo, en este caso dicha entrada es activa a NIVEL BAJO, ya que el dispositivo se activa cuando dicha entrada recibe un

-

~1

~.

,....j:~: l __..:)

........ .

Circuitos Comhillac:"cmules MSI .5

Ejemplo de Decodificador completo de 3 a 8 lneas: CIRClJlTO 74Xl38

X.

L H. H H H

H H H

H

:ENA.BLE

1-l ;{

~ L i.: L L [ L

t _

INPU.TS

H X

. L. 1 .. L L L L

SELE.C B

!

-

Circuitos Combirw.cimzulcs MSI '--4

REALIZACIN DE FUNCIONES CON DECODIFICADORES

Un circuito decodificador completo genera todos los productos fundamentales (mintnninos) de las variables de entrada.

Cundo las salidas del decodificador son activas a nivel bajo, para realizar la funcin en suma de productos basta con conectar las salidas correspondientes a los mintrminos de la funcin usando puertas NAND:

Por ejemplo: F(X,Y,Z) = :L rri(O, 3, 6)

z y X

vcc

GND Gl

G2A G2B

3/8

DI D2 D3 LJ-------, D4 D5 D6r.}---~ D7

F

A veces puede ocurrir que necesitemos decodificar ms lneas de las que nos permite nuestro circuito, se bebe entonces construir un decodificador de mayor tamao usando decodificadores de menor tamao:

Por ejemplo para 4 bits (X,Y,Z,W)

w 3/8

A z B y e l X D3 X=O

_ VC.f Gl

G2A G2B

3/8 A B D1 e D2

D3 X=1

Gl G2A G2B

GND

' j - ~

--

-

)_

)

X "'\; ......

CircLitos Comhiizac:iollales ii1S! 5

CON'lERTIDORES DE CDIGOS Son circuitos Codificadores/Decodificadores que convierten los datos de un

cdigo a otro.

El circuito 74X42 es un convertidor de BCD a Decimal (de 4 a 10 lneas).

NO.

-~:. .. il .

.t'

_: .

.&w::iid

L .. L !,. !, 1.,

.:i .. L

L ,Hi .Jf :H, :H:

!+

A. t L,

.'L L 1.. H 1.. H H e ;.,, t H H 1-i H '\. 1;,

'1. J;; i . H .\.. rl H :L h . L )i H .w .

:O' . L.

H.

FUN'C110N TARLE

H !. 8 H H 1-l H 1-i

'. H .H . H H 11 H H

:._H

:H 8 . l-.{ H

~ H ~ , t H ~ l. ti H ,.; H

!l H \H H H H H H ~. H 'H H lH H H H

a 7 HJ H

H H H H H L

.:

H . H

H .H .

~ 1 ;_____J. .. . . 'P'~,.----- JJ 1 ,___y--...____,.;- .

. JiL__~ /\ ~:-.---~. ~!M= ~)~. . .... : . ....:. . ~~ tri==.~t:r~ :;! . ::,...._ .. - .:i

1d B -----l

e

LV~ JfEff=gc:):;;..___ _ .. ,6 . ~~:~--1l=5!ia~==\r::.;..~--9- 7 , . -y L J~gf.:.__=~B~:-__ lo. ,e

-

Convertidor Binario- Gray.

' : .. .: ':

: . .. , ... .

.. ..

.. _.,:~ ... --~.. . .. _:,.:.-.,: .. ... , _:: ~ ::.

. --~ . ' ' . . ...

..

~

. ""

~

: ,.-..

-

)::,

Convertidor BCD~ binario (7 4184).

-~ ~~G~--~E~----~D~----~C~--~8~- ----~AL~ . l

y:aW Y7J Y2 Y3

""\ Y2 Y3 Y-4- Y-5 Y.fi Y7 / GND ~--------~----~--~~--------------------DUT?UTS

-

Convertidor binario- BCD (7 4185).

{~4f ~

~ i ~ .. _.~,~_.. ' ~~..:.:: 11 '' ~ .. : :,.....: '9~--' . _..__ ___ __,.,.. .. ~; j

-

1 ~

L

d .

.L.

,(

l. ........

1 >'--

Circuitos Cvmh inacionul~s J'v!SI

El circuito 74X47 es un convertidor de BCD a 7-sernnentos (de 4 a 7 lneas) . Permite visualiz3.r en un display de 7-segmentos el dgito decimal correspondiente al BCD. Son circuitos drivers.

Los visualizadores estn formados por siete LEDs (Light .t:mmer Diode), que son dispositivos que emiten luz cuando la corriente que los atraviesa excede de un cierto valor (al igual que un diodo normal conduce cuando se supera una determinada tensin entre sus bornes), de ah que para su excitacin se necesiten dispositivos que proporcionen corriente suficiente. Existen dos tipos de visualizadores con LEDs principalmente. Los de nodo comn y-los de ctodo comn . Los primeros se usan cuando el decodificador tiene salidas activas a nivel bajo, mientras que los segundos son para los decodificadores con salidas activas a nivel alto.

vcc

1 NODO COMN

Otros visualizadores muy usados son los LCD (Liquid Crystal Display) que no estn formados por diodos sino por una serie de plaquitas conductoras capaces de excitar un lquido que hay entre ellas.

Smbolo lgico y explicacin de los terminales de I/0:

SALIDAS a display 7 -seg nodo comn

(conexin mediante R=l5.0.Q)

Asignacin numrica de las entradas y resultado de la visualizacin

4 6 .7 9 \O

-

CIRCUITO DECODIFICADOR DE 7 SEGl'VIENTOS 7447

V~-

~ --------=----=--------------'~ L T. Es fa prueba de lmparas . s se coloca a masa se encienden todos los segmentos, sirve para comprobar si hay alguno fundido.

RBL Sirve para apagar todos los segmentos cuando est a nivel bajo y las entradas A, 8, y e se encuentran a nivel bajo. Esto se utiliza para no ver los ceros a la izquierda aJando se acoplan varios integrados . La entrada de prueba de lmparas debe de estar a nivel alto para el correcto funcionamiento de esta entrada.

. ~

81/RBO. Es una saiida que muestra nivel alto, sa!vo que RBI, A, B, e y D se encuentren a nivel bajo, en este casos .. ,~ colocar a nivel Sin1e varios drcuitos as visualizar ms

... . ----.

-

A

\ A

A A

~

A A .J.,

A. A )" A A

~ ~ A

A )._,_ A

. ~

A A

1 ,...___

.-L.

?---.

l ~

J....

.-L. . 1

'"''

, .. _A:

;:; ; )

-

:~. . ...

~

-

.l

1 A

,......_

~ :

{, ?-'

-

1 /-

-~

~-.

~ - -

Circuitos CombiHacionales J'vfSJ

En la siguiente figura se representa el diagrama lgico de un codificador completo de Decimal a BCD natural, junto a su tabla de funcionamiento.

11 12 13 14 15 16 17 18 19 A B e D l1 Dec/BCD o Q o o .o o o o o o o o o 1 o o o o o o o o o o o 1 o 1 o o o o o o o o o 1 o o o 1 o o o o o o o o 1 1 o o o 1 o o o o o o 1 o o o o o o 1 o o o o o 1 o 1 o o o o o 1 o o o o 1 1 o

l2 13 A 14 B 15 e 16 l7 D

o o o o o o 1 o o o 1 1 1 18 o o o o o o o 1 o 1 o o o 19 o o o o o o o o 1 1 o o 1

Por otro lado la figura siguiente representa el diagrama lgico del circuito 74147, que es un codificador de prioridad de Decimal a BCD natural; en la tabla de funcionamiento adjlmta se puede notar la diferencia con el anterior.

/il 11.2 /13 /14 /15 116 /17 X X X X X X X V X v X X X X J'\.

-"'-

X X X X X X o X X X X X o 1 X X X X o 1. 1 X X X o 1 1 1 X X o 1 1 1 1 X o 1 1 1 1 1 o 1 1 1 1 1 1 1 1 1 1 1 1 1

.-

/18 /19 /A X o o o 1 o 1 1 1 1 1 1 1 1 1 1 1

. 1 1 1 1 1 1 1 1 1 1 1 1

lB /C 1 1 1 1 o o o o o 1 o 1 1 o 1 o l 1 1 1

ID o 1 o 1 o 1 o 1 o 1

Dec/BCD

!A lB iC ID

-

Cirwitos Combillacionules 1\JSJ

Cuando se trata de establecer la prioridad con mayor nmero de bits, es preciso recurrir a la asociacin de codificadores. El siguiente diacrama muestra un

~ ~

codificador de prioridad de 16 lneas a 4, usando codificadores de prioridad 74148, de 8 a 3 lneas .

{.1N[8-15J

/EI: Habilitacin /GS : es O cuando el dispositivo est

habilitado y una o ms de sus entrada? est activa

lEO: salida para habilitar otro codificador de ms baja prioridad

~ . . . . . ) /RAO . ;

'------- :~:/

~o .

r-----'-C,....:4 08 '>z = :/\1

\ Jl~ . )~":---'

_)i

/JN[0,-:7] .-------__J ..::.. !t. ~12 :.=:13 .

, . :.=:I~: . . ::c:l~ L::::l6" L::::!7 .'--~:::El

Ao,----l A1 o-,- ---+----' f\26~, --+---' .

GSo EO.:)~

----~ 7408/P..A3

.----------i().

~

/-"'~ : -~, J-....

;:=.; ,..-.._ ... u:

. /--...

-

-_.,.:--..,:

Circuito lgico d~~ cnnexionado dd 74143 ~=.

-

ueiDa de la_s patiHas de! integr.1do 7 4148 E n~rada.s d eo d.a"t:os Salid.a

:r--------------------. d-e d.al:"C>:S

Tab:O.a de funcionamiento dei 74143

;~

-

_-;., ..... ___:::-~:. :

Ccdicador Decimal ~ BCD

L~. t . ~ ~- . 4) H . f

i.~l ti ..

' .. "('i . F

,. f : ~~ ., ..

,.

. l ;:..~ .l. ( j

- CODIFlCAOOR DE TECLADO HE.XADEClMAL CON MEMOR.lZACiON Y ANTIRREBOTE INFORMA CUANDO TIENE LA CODIFlCACON DEL~ TECLA MEDIANTE UN PULSO DE CORTA DURAClN DE TIEMPO SOBRE PA11LL.

-

--- ---- -------- -

1 ~

:.,

""'

1 r-'-.

1 ~ -

...... : .. .

. .- :: .:,_:.~ .. :~ -:;=- . . :~~.; :.. ;_:. :.::.: : : : ::~ -

. . -:. -~ r;:; . p;.:;:"'"' eu:; .

,, .. ...

': ,:'

-

Circuitos Combinacionales \JSI

IYIUL TIPLEXORES

l\!Iultiplexar es pasar informacin de "muchos" canales o lneas a "pocos" canales ci lneas.

Un lYillLTIPLEXOR (MUX) es un circuito ., combinacional que selecciona una entrada y la transfiere a la salida. La seleccin de la entrada, o dato, se realiza segn un conjunto de valores de las variables de control.

1

Poseen por tanto, n entradas de seleccin, para 2n entrada de datos, proporcionando dos salidas: una para el dato directo y otra para el dato negado ..

A continuacin se presenta la tabla de funcionamiento y el Smbolo lgico estndar para un multiplexor de 8 a 1 lneas. Se trata del circuito 74Xl51, con entrada de habilitacin activa a nivel bajo.

FUNcTIONTASLE INPUTS

OUTPUTS SELECT ST:OBE e B.

.A G'" y w X X X. H L H' L .l l l bu DO l l H L Dl 01 L H L ' L 02 :b2 L H ri l 03. 03 H L L .L Q4 54

-H l H L os [)S H H L L Q.E). 06 ti H H L 07. B7

H = h1gh leve!, l = law lev.e.l,. X. = irrelevaot. . Do: Dl, . .... D7 = ltie fevcl of tn~ resiective:.O. n;jut

G' ' .7 K MUX it' EN'

A o" . '1:0 ~} G_Q : 9 ,. e: .4

- .{' DO .o 5 D1

a y i. 6 2 ~ w 02, 2

'1 03 3

'1:5 04

14 4 05

.5 13'

os 6 1'2

07 ' 7

1 ._.,

._ ~~ ..

. --~

'-

!:.:~-.:= . _,..-....

}: .J ---

..:-. -.

. '

-:-

,/""

~ :

-~: :.-=-

-.:;.. .-...

-

l _....._._

;;) )

-----

_;l;

74151 DA"TAIN.P"V"TS

~--------~~~----------~ O.ATA S.LECT

r-~----~-~~----~~

~----------~~r------------J '-------.:>.,r,.....----" ~,..,.,._~':TS -O(.J 'T-?-UT-S

74153

:S'T RO!S!E B "'h3 "S-E"L~;CT

~,..-_...,,...,_ ___ ~ ..,,-----.Jfi"-._"----. ...

45

'----.,.,..,..----"

i'tN?UTS OUT?UT

... -~ . ! "/ ' - ~.

-

Circuitos Comhimu:imwles tldSI

Existen en el mercado diferentes multiplexores.

El siguiente corresponde al 74153, que es un circuito :NISI con dos Mux de 4 a 1 lneas . . A los Ivu."'< se les suele llamar tambin selectores de datos. As este sera un selector de datos 1-de- 4 (ya que selecciona un dato de cuatro disponibles) .

.FUNcTON TABLE U-,PUTS'

,OUTPIJT SEL.EC,T DATA STROBE ;: Y.

B A' :o C1 "C2: C3 X x X X: X .X H. L L L L X X :X L. L L L H X X X L H L H- -~ !., X X 1., L L . H X. . H .X 'X L H H L x X L X L L H L. X :X .H X l H H H x X X L L l

-

H H X 'x X H L H

]"" "

'1 =""""'==- . n

H!l -': !::_< -------f--i-f'-;-~_j ...,~ "';_: .... _fi ___ _

' '"'' it r:,:='::":-:-::::o .::;_~ .134

-,l! 'O .

1;: ~ .J: ~ C:2 -~-~1-:2

o. ll Lik-...::i==.,-~ i,'l(

El diagrama lgico sobre estas lneas corresponde a la configuracin interior del dispositivo arriba descrito, lo que nos puede dar una idea de la diferencia entre los circuitos SSI y los MSI.

r'! . . ~ ~ ,; - ,

._;......

_ .. , . .---.,

-:: -

:-:--

/"""-.

._ . ....--

: ;-.

-.:.--..

:-~--~

-

1 ----"

.\ ..:_

1 ~.

) ~

Circui/os Comhinacimw.les i'v!SJ

Un multiplexor muy usado es el 74157 (El 74158 es una versin del primero cc11 las salidas activas a nivel bajo). Se trata de un circuito con cudmple multiplexor de dos a una lneas:

"G 15

AIB

,2 1A

.3 1E!.

.5 2A

6 2i3

i1 3k-

38 1P ;;

4A

'!Ei 13

FUNCTiON TABLE l~,ff'UT~>

.;.....;, -

DATA G A/8

A B H X V . V ~ !~. L L L X L L H X t H "' .L "':'." -L H X H

~ALS157:JL, s~:u4As157

t (;1 J : Mux:

1

4 iY

7 2Y

9 '3Y'

i'" ... 4Y

OUTPUTY

.ALSt57A. 'AL$15.8-SN74AS157 : SN74A$1;5$.

L H L H H L L H H L

--

15

-

Circuiios Cambinacionu.fes ~fSI

EXTENSIN DE lYIULTIPLEXORES Corno siempre, cuando no se dispone del nmero necesario de entradas en un

solo dispositivo, hay que recurrir a asociar dispositivos de menor nmero de . -

entradas para obtener uno mayor.

Vamos a construir un M1JX de 16:1 usando l\lfUX de 4:1. La asociacin es muy similar a la que se hace con los decodificadores, pero

cambian la dispos.icin de los MSB y LSB (bits ms significativos y menos significativos).

S3 S2 Sl SO ~ i lf ~

----t-----1~-} (; ~ _,

----r ~ Eit i;t\.ii>

DO --+-+---t---l o. - - .

-2

r- .

- a: ,.,_ !:-', ---~

- .--

'--- n'\ :

'----t--- D. '-----+--...,..,_ . r-----+--- ~

- '" '

.-:.

...,. . d. gn

Dato 1 de 16

?, - ~:;::-~

-~:--. . _;...._

. ;

..-. .

.-----.

:- .

;; ~ ..:.~

-::

-

j

------

) ~

1 ......._

-~ J .~

),

Circuitos Combinacionales ;\.JSJ ! ':

3. Hacemos el diagrama lgico del circuito colocando den las entradas de datos io que la tabla nos indique.

Ej: Nuestra tabla nos dice que en la entrada IO de nuestro :tviUX, debewos colocar un 1; que en la 11, un O; ...

Nos debe quedar un circuito como el de la figura:

vcc

T~E ~ ~~~!o :~/A ----< 11

)-,-1>-_,.j. . //O'_.J_,_--4---1 12 v-d404 t~ ~------------4-4---~lo

----< 16 .L--..___ 17

D ~---------1,-_j SO e : _}'----------+----l s1 B 12). --________ ..;____J S2

.Ui

:7 ~f - : .. ::

74151 P.:

-

Circuitos Combi11aCi01wies MSI u

EJERCICIO DE MUX

Para familiarizarnos con el empleo de 1vlUX, deduzcamos la funcin que realiza el siguiente circuito

vccQ. 7 co --------~-------4~------------------~ Y ,roo----------------+--------------------'-, X ::o~ .. -----------------,

VV' eJ.: --------------+-+-+---1 so . v;~ SJ

r: -EA ;_______;,; : ,_: :_.: IDA

' 4 . . . ~ 11.A Z~1----. ' 12.1\

' ~:__.: 13f\

~ ~~:: '

.1 ,________: llB . ZB~---. e,_.'-4--+4-+-----1128: ',

o-- I;:J,El

'-+-+-+--1 so ~-+-----" s:r ~EA;

: ;..:... e--::: IO.Ai :..:....i.-. nA ZA.1--~

i~I2A. .,_---t---i 13A

;~:;EB : . . 108

'-'-----+---111 e za 1---....J '------1'---!128 '

n-----13.8 GN D., - ', L' :::-:-:-::=::::~ ~ 74153

:G~JO .. :v .

. cr' EB. =:los . - 118. ZB......, __: 128 . . --:; ]38:

. 7.4153

._:.-

--

._;.:.o..._

. ..:..._

-: :~

.. .:;-....

. ~

- ~

.;:: ..

-

1 _..-,

) r'-

,.J

_,

- ~,

r .

Circuitos CmnhiTwciollales !viS!

DEIYIUL TIPLEXORES

En realidad no existen como tales, smo que v1enen definidos por los decodificadores/demultiplexores.

La funcin que debe realizar es la inversa de la que realiza el 1v1UX, o sea, debemos seleccioriar una salida por donde transmitir el dato de la entrada.

Por tanto, el circuito constar de 1 entrada de datos, n entradas de seleccin de salida, y 2n salidas.

El Decodificador/DEMUX 74138 que ya conocemos utiliza su entrada de habilitacin Gl para entrada de Datos: -

G1

H H H -H-H .H H

INPIJTS

G2A , !i2:B fi :x x H )( ,X L l.. l l L ' L L --L [ l l :L \,. \,.

_L L

X X >; L L l L , -H .

',li H

X

X L. L

l. L

tt " :r.-1,

,.A- , YO.

X H X H :

-

SELECTORES DE DALTOS. DEi'/1UL TlPLEXORES

_ :~~ Realiza ia funcin cc.ntrali.a aJ mu!tipfexDF. Tornaate:S de un.linay +OS~ ':~::d1strili~y-e a un dBrefmffieda nmero De Hneas de sa8da. . . . .

. ,

.:

. -~

.. :;:_ . -.

.. ..--...

. .---...

-

~-------............. -~. --

1 ~

i ""'

) _...

-

74155 .... -

:: ............_ -::;

,.....,.

f:~;;:.:...,

f. .. .. . ~

741.39 D.ATA~"'T;S

------------~~----------~ ;y-.

1 .

.~: :: ,...-...., ...:

... . ,.--..;

. ...--.:.

..

. ~:-...

_.,,. .. ~

-

1

------

' .A

J) .J? J: ~ -

Circuitos Arinnticos

CIRCUITOS AR1TlV1TICOS Son dispositivos lYISI que pueden reabzar operaciones aritmticas (suma, resta, multiplicacin y divisin) con nmeros binarios. De todos los dispositivos, nos centraremos en los comparadores de magnitud, detectores y generadores de paridad, sumadores yALU's.

Comparadores de Magnitud

Son circuitos que comparan el valor binario de dos nmeros, proporcionando informacin de cul es mayor, menor, o si ambos son iguales. Son sistemas muy usados en ingeniera. Su bloque y tabla de funcionamiento bsico son los siguientes

A B A>B A=B AB

A=B A

-

. )

! ~

-------- -

,_._ ..

. . :~ .. ~- . .

-

Circuitos A..ritlneticos

'r Las Salidas del comparador se pueden deducir de las siguientes expresiones lgicas :

(A>B) =(No A>No B) or [(No A=No B) and (AJn>Bin)] (A=B) =(No A=No B) and (Ain=Bin) (A

-

1 ~

...

A

Circuitos Aritmticos

La extensin de esta construccin a comparadores de mayor nmero de bits es bien sencilla.

fl,[0- '15) 1

E{-15j U7 UR p,(l AO ,A::-1. i~O il.'l .~ A';) ,il:l p\--;

1\ '" ~~6 A2

,!\3 r\L "~ A3 A

,ll..in6in

74LS85 74LS35

.~ ..

-

CircuitO$ .A.rilmticos

El siguiente circuito es tma aplicacin completa de comparadores, en la que se comparan tres nmeros codificados en BCD (palabras de 4 bits) y se escoge el menor. Para ello se comparan dos nmeros y se torna el menor y ste se compara con el tercero; se usa para "transmitir" el nmero seleccionado un 1vfUX cudruple de 2 a 1 lneas (se h~ usado simbologa segn el estndar de IEEE):

A[0-3] B[0-3]

1 ~ EN COMP.: ~:l

- ol BO ,. r "{ MUX

a A - (p ~ AO i . f; "t.J t ...___ Bl P

-

! """"'

.,.!:.'

Circuitos ,"ill.t111eticos

Detectores y generadores de Paridad

Son circuitos MSI que detectan si en la entrada hay un nmero par o impar de '~unos", o sea, detectan la paridad de una palabra digital. Se basan en la funcin EX-OR. St..:. aplicacin principal se basa en la transmisin .y deteccin de cdigos en las comunicaciones digitales. Un tipo de cdigo muy usado en las transmisiones digitales es aquel que a una palabra digital le aade un bit que indique la paridad de la palabra. Cuando nuestro circuito genere el hit de paridad, funcionar como transmisor, y cuando tenga que detectarlo, funcionar como receptor. Supongamos que vamos a trasmitir la palabra de 7 bits [1 O 1111 O] con paridad par, el bit que debemos aadir debe ser un 1, para que el total de unos sea par.

Como Transmisor: 1011110 1 n de unos 6

En el receptor recibimos una palabra de 8 bits [ 1 O 1111 O 1] detectamos su paridad y si es par (como ocurre en este caso), admitimos la palabra como correcta.

El circuito de la figura corresponde al 74ALS280

Al A a

'S

10 e

......

.1 D

2 ~-

13 F

1 G

. .i'\ :...::,

H 4

J

.

Nb, OF IN,PUTS A....:1

! t, s; s, 7, 'B L

OUTP.IJTS

H

1--------.! EVEN

I:ODD

-

Circuitos .'\.rit:mticos

Sumadores

Un sumador es lm circuito que realiza la suma de dos palabras binarias. Es distinta de la operacin OR y con la que no nos debemos confundir. Est basada en la suma decimal que conocemos tan bien:

1 2 3

01 10 1 1

2 2 4

10 10

lOO Como vemos la suma de nmeros binarios de un bit nos puede dar un nmero binario de tres bits. As un sumador de dos bits deberia tener 2 entradas y tres salidas. A este bit ms significativo en la salida se le conoce como el acarreo (parecido al "me llevo una" de la suma decimal).

Asignemos una tabla de funcionamiento y un smbolo a un dispositivo que realice esta operacin, al que se le suele denominar medio sumador:

AB CARRY A+B L 00 o o A- ~A+B o 1 o 1 1 o o 1 B- -Cout 1 1 1 o

-

A la salida A+B, se le conoce tambin como media suma (HA) . Cout, indica el acarreo de salida (carry out). Esta salida se puede usar para conectar en cascada distintos sumadores, de manera que podamos sumar palabras de ms de un bit. Para ello necesitamos que el circuito disponga de una entrada extra por donde podamos informarle de la suma de los bits anteriores. A este dispositivo se le denomina sumador completo :

A - ' ,__A+B

B - . L

:-- Cout Cin-

."" ~ .

: -------

-'

:. ~

~:~ ---:...:.

-

Semisumador

. .J.l

, .

.. ;.!~

:, ~.

-

Circuitos .-\Ji 1m ticos

Su tabla de funcionamiento seria la siguiente:

AB Cin Cout A+B 00 o o o 00 1 o 1 o 1 o o ., 1 o 1 1 1 o 1 o o o 1 1 o 1 1 o 1 1 o 1 o 1 1 1 1 1

Este sumador completo constituye el bloque bsico para sumar palabras de mayor nmero de bits .. Como ejemplo el siguiente circuito suma dos palabras de seis bits A[0-5] y B[0-5] para darnos una palabra de siete bits S[0-6], los seis menos significativos corresponden a la media suma y el MSB es el del acarreo de salida .

A . [0-51

8 [0-5] surn1 su m: sum3 co co co

f- .il:l SUMl ~...___ A1 SUM1 ~'-- .!1.,1 ~M1~ 81 81 81 '- . .U.2 SUM2 - ,,..., SUM2 L.-- .~2 SUM2 . S~ .~.:;.

8'"' C2 - 82 C2 - 82 ~.., . . _b

..:. L_.,_

7482 7482 7 4J=] '') 1 ' -~ sro

- :5] .,.

1]

La suma que realiza este circuito se suele denominar suma con propagacin de acarreo, puesto que como se ve, el acarreo se , prop~ga de. un sumacior al siguiente . .. Aqu el acarreo se propaga en serie, pero puede propagarse en paralelo mediante un circuito de propagacin del acarreo que veremos ms adelante.

. :.:..:...:..

-~

.. ~

::.

-

1 -'--

1 --'.

.1

.1

J

. )

---

..1

. =~

.)._ .. J... :

Circuitos Aritmticos

Este circuito suma 16 bits con propagacin de acarreo sen e, usando sumadores completos de 4 bits (74LS283).

:A.rn~ 151

,A ,O A.l

.. ~'l. .. ~.2

-A:1. .A;.3

. A.4 .A:O

., .... ,:J .A.l -.~.b ll'J :.~.l ,r.:r .~.u

.84 81] d.::J 81 ob 62 tf'

. , 1 8.3

Cl

:30 s

..

so 81 C""'"'l ...:J" C.':' J __:.e_. .

ca l4L2:iLl:Kj .

0 1. 6 .. r-.,-~ ..... \_;., . . == .::n.f.J . '.'t~-i _. ,_, .. - J c1 cd ~-------i . ,11---~r-------

7 4LS283: ~[0-"15l _-(1

Si el tiempo que tarda el circuito sumador en obtener, a partir de los datos de entrada, los valores de la salida lo denominamos 'C, el tiempo que se tarda en obtener la palabra S[0-16] como la suma binaria de A[0-15] y B[0-15], con este circuito es 4'T .

El smbolo estndar del 74LS283 es el que se tiene a continuacin .

e o l~-c-l _____ --.;.

-

1 .-!..._

.1

) ..

Circuitos .~tmticos

Los sumadores se pueden aplicar tambin a la conversin de cdigos, ya que en muchas codificaciones se usa la suma de una palabra deteur.tinada para obtener otro cdigo distinto.

Por ejemplo, para obrener una palabra dei cdigo ,BCD-exceso3, basta sumar ia palabra 0011 al nmero BCD-natural.

Otros casos no son tan triviales; por ejemplo, veamos la realizacin de un convertidor de cdigo BCD-natural a BCD-Aiken, usando un circuito sumador de 4 bits y puertas lgicas:

BCD-natural Palabra para conyertir n AJ A2 Al AO B3 B2 Bl BO S3 o o o o o o o o o o 1 o o o 1 o o o o o 2 o o 1 o o o o o o 3 o o 1 l o o o o o 4 o 1 o o o o o o o 5 o 1 o 1 o 1 1 o 1 6 o 1 1 o o 1 1 o 1 7 o 1 1 1 o 1 1 o 1 8 1 o o o o 1 1 o 1 9 1 o o 1 o 1 1 o 1 X 1 o 1 o X X X X X

De la tabla de funcionamiento se obtienen B a partir de las A: > B3 = Bo =O > B 1 = B2 = A3 + A2A1 + A2Ao

Y el circuito queda:

~ ~ A J } r A2 ~ A3 .al 3

3J~ e~

BCD-Aiken S2 SI so o o o o o 1 o 1 o o 1 1 1 o o o 1 1 1 o o 1 o 1 1 1 o 1 1 1 X X V ..r>..

, ..

So S s2 s3

-

Circuitos A.rib.nticos

Restadores

No existen en realidad, sino que se realizan mediante sumadores, ya que la resta de dos nmeros es la sunia de uno con el negativo del otro. El negativo de un nmero binario se puede obtener en comple:w.entc a une (inversin. de todos los bits uno a uno); o, en complemento a dos (se aade un bit de si~o).

Este circuito realiza la resta de A[0-3] yB[0-3] en complemento a uno:

: "} ~

'{: ":""' So ,__ S _3 : ,_ Sz r--.... :}~ r- s3 K K _..-ca -- CL

Y este otro es un sumador/restador .de las palabras de 3 bits A[0-2] y B[0-2], en complemento a dos, ntese el uso del bit de signo. La entrada SL es O para obtener A+B y 1 para obtener A-B.

~-= ____ ___1?1 :.~ . _. olso A"l r~ , . . . . . S

As--__;_---------~ Bo ------------~

Bs

SL --------'

l. ~

, --..

.--

.-.:!. -~:::::

-

1.

..iii . , . .7' ' ~! f.! . -L~1

-~~!.~\ ,;

: '11 ~i '"" 1;.

."1

-

Como se puede comprobar, el resultado es el nmero decimal 12 representado en BCD natural.

El complemento a nueve de un nmero decimal de una sola cifra es el resultado de restar dicho nume ro a nueve. Por ejemplo, el complemento a nueve de dos

'/"'-.

e) Que l~ suma ge?ere acarreo . ~n este caso, __ es ser siete, ya que 9 _ 2 = 7. Para representar nme- ---t:l-:rn.G.J.en-tl~Gel)d.I:.J-G-b.:lc~~rn.a_c.o.r.r.e.c.cJ..O.l1. ___ ros-ne2a-t:i.-vo s -se-ut:il:i:za- ce m o-en-e 1-cas 0 de resta bina-

que en el caso anterior, es decir, sumar al ptimer ria el -bit de sicrno . '

-. '-.

resultado el nmero 0110. Ejemplos: "' Ejemplo: sumar 9 + 8:

.. ~

1001 + 1000 1 0001

+ 011'0 (Correr.:cin) 1 0111

El resultado definitivo es el nmero 17 codifi-cado en BCD naturaL

Para completar la expli~acin del proceso realizare-mos la suma siguiente, formada por dos operandos de cuatro cifras cada uno:

1-+-, 1 0011 0100 1000 0001

+ 0010 0110 1000 0101 --- --- --

0110 1011 1 0000 0110 348L + 0110 0110 (Correccin)

- --

+ 2685 1 OllO 6166 0110 0001 0110 0110

Como se puede comprobar, los bits de acarreo . se agregan a la suma de la cifra de peso inmediato supe-oor.

4.5.2. Resta en BCD natrn:al ....

Para realizar una resta en BCD natural, se suma al minuendo el complemenro a nueve de cada una de las cifras del sustraendo.

,.,

a) Restar 1.829 a 2.362: - ~

ES 1 1 o 0010 0011 0110 0010 ~:-=:..; ....

+ 1 1000 . 0001 0111 0000 (~;.1 ~ ---

--

10 1010 0101 1101 0010 . : 1 + 0110 0110 ( Corr~ccin)

---: "

2362 1 0000 1 0011 - 1829 L-------------- + 1 ........_

0533 o 0000 0101 0011 0011

----~~:. El O del bit de si~o indica que el resultado '"""

(533) es positivo. El arrastre del bit de signo, si existe se suma a la cifra de menor peso. . ) . ' .. . . . . .

b) Restar 2.362 a 1.829: :>.

En este caso, el bit de signo vale 1, indicandO, de :, r--o_ esta manera, que el resultado es negativo y que { .....__ queda expresado en la forma de complemenro a .

. ....._

nueve.

4J5. DliSEN DE SUMADORES Y RESTADORES BCD .,..._ ___________ ....:...__:...__.:_:_:_:.::.:....:.:::.-=-:..:=-.:..::::.:=-=----------- ( ';___

~8~""r.~~acv 'ati:ai para.~ das: sumarid65. Cada.~ . Uno.:; . '. .. .: ... ~~~!?Bar:: :ur.r: circuitocque:, permita ... obtener en. binario .el:'.

p m,on. t,-, ' nueve:de. unnmero.decimaL

-~ 1 ......

-

1 -----.._

1 ~

1 ~

.

--'---

1

J

; ~,

.J..

4.6.1. Proeeso de diseo de 1m. Slunador BCD natural de dos nmeros

Todos les circuitos que vamos a definir e11 ste y en lo$ siguientes apartados tienen como elemento bsico el dispositivo 7483.

En la Tabla 4.4 aparecen las veinte combinaciones que se pueden obtener al sumar dos nmeros en BCD. Tngase en cuenta que el valor mximo de cada suman-do ser nueve, pero cabe la posibilidad de que exista acarreo procedente de la operacin anterior, con lo cual el valor mximo de la suma ser: 9 + 9 + 1 = 19. La combinacin que completa las veinte que aparecen en la tabla ser la correspondiente a la suma del valor O. En la parte izquierda de dicha tabla aparece el resulta-do de la suma expresada en binario, y en la derecha, el valor corregido, o resultado BCD. Como se sabe, los ltimos diez resultados binarios necesitan correccin. bien porque son combinaciones no empleadas en BCD o bien porque presentan acarreo.

Para diferenciar el acarreo procedente de los suma-dores binarios del acarreo del sumador BCD natural hemos representado al primero de la siguiente manera:

e~ . Del mismo modo, los resultados de la suma, a la salida del primer sumador, antes de la correccin se representan como S~, S~, S~ y S~.

Reduciendo mediante el mtodo de Karnaugh, se obtiene el siguiente valor de e4 :

e4 = e~ + S~ S~ + S~ s; = e~ S~ S~ S~ s;

o o o o o o o o o o o o o o o o l 1 1 1

Tabla 4.4. Resultados posibles al sumar dos nmeros expresados en BCD

o o o o o o o o o o o o 1 o o o o 1 o o 1 o o o o .t o o o 1 1 o o o 1 1 o 1 o o o o 1 o o o 1 o 1 o o 1 o 1 o 1 1 o o o 1 1 o o 1 1 1 o o 1 1 1 1 o o o o 1 o o o 1 o o 1 o 1 o o 1 1 o 1 o 1 o o o o 1 o 1 1 1 o o o 1 1 1 o o 1 o o 1 o 1 1 o 1 1 o o 1 l 1 1 1 o 1 o 1 o o 1 1 1 1 1 o 1 o 1 o o o o 1 o 1 1 o o o o l 1 o 1 1 1 o o l o 1 o o o o o 1 1 1 o o 1

o 1 2 '

4 S 6 7 8 9

10 11 1:2 13 14 15 16 17 13 19

_,:. ) ---:-- -,-.

L1 salida C4 se utiliza para indic:u el acarreo de la s urna y, adems, para realizar la correccin a partir de la combinacin correspondiente al nmero die= de la Tabla 4.4. La funcin se implementa mediante bs cu

-

4- 6.2. Proceso de diseo de un circuito zenerador

.....

e mplemento a nueve

Como se ha sealado en el Apartado 4.5.2, la resta BCD se realiza sumando al minuendo el sustraendo complementado a nueve. Por esta razn, es imprescin-dible, antes de efectuar la operacin, colocar un circui-to combinacional que complemente. el sustraendo. El diseo de este circuito es sencillo, siendo el proceso el mismo que hemos seguido en tantas ocasiones. En primer lugar, rebcionaremos las entradas con las sali-das, tal como se muestra en la Tabla 4.5. Las funciones que se infieren de la tabla son las siguientes:

B 1 li1 B z b2

B 3 = b352 + 3b2 B 4 54 53 52 = b4 ,

Tabla 4.5. Tabla de verdad y ecuaciones correspondierltes a un generador

de complemento a nueve

o 9 o o o o 1 o o 1 1 8 o o o 1 1 o o o 2 7 o o 1 o o 1 1 1 3 6 o o 1 1 o 1 1 o 4 ) o 1 o o o 1 o l 5 4 o 1 o 1 o 1 o o 6 3 o 1 1 o .o o 1 1 7 2 o 1 1 1 o o 1 o 8 1 o o o o o o o 1 9 o 1 o o o o o o

El_ diagr;J.ma lgico resultante es el que se muestra en la FJO'ura 4 1-, b 1

"' . .:. y su representacwn s1m o 1ca es la que aparece en la F igura 4.13.

1n4o4

b, ------------~,-~r- ~2 _____________ a, b2-----~--~----------------------l 82 , 1n4a5

b2_-__ j_CR.....!.:?_;:~:: 1/7410

Generador de complemento a nueve.

b,

1 1 1 1 Generador de

complemento . :. ~- :-:,~, --~: ,_.-_: .. -:- :-:- '.. .

.-., a:iiueve ' - i:

B,

Figura 4.13. Representacin simblica de un generador de complementoa .nueve.

' 1

4.6.3. Proceso de diseo de u.n restador BCD para nm.eros .de dos digitos cada uno

La operacwn de resta se realizar, en este caso, sin utilizar bits de si!!no. Co:i:no se recordar, cuando el . . resultado de la operacin es positivo, se genera b:it de ,:, acarreo en la suma correspondiente a las cifras (o bits) ms significativos. Cuando esto ocurre, el bit debe aa-dirse (sumarse) a las cifras (o bits) de menor peso. Para ello es necesario conectar la salida C4 del bloque de las decenas a la entrada C0 del bloque de las unidades.

PDr otra parte, el sustraendo se complementar an-tes de ser aplicado al sumador. El resultado es el que se >-'--muestra en la Figura 4.14.

Cuando el resultado de la resta es negativo, la solu-cin queda expresada en forma de complemento a ne-ve, sin que se produzca acarreo en la ltima cifra.

84 ' ' 83. .8z a, . 8~ 82 8:!. B, a~ a2 a2 ,,

1 r a3 az a,

1

e,! :: ,' . ' :.':~ > ' CQ .. Sumador Co .. 1

BCD , . . 1

...

DECENAS UNIDADES

Figura 4.1 4. Restador BCD natural.

{~~

-:_.

. --.

r..

-

1 A

l

' -~

' .~

.L

' .

.1

. ..L.

. ..f:.l

J ;

Circuitos Aritmticos

ALU's

ALU son las siglas de Aritmethic Logic Unit, o sea, Unidad Lgico Aritmtica. Se trata de un circuito MSI que puede realizar diferentes operaciones aritmticas y lgicas con dos palabras den bits.

El ms conocido es 74LS181 , que es una ALU de 4 bits, que puede realizar hasta 32 funciones diferentes\ (16 lgicas y 16 aritmticas). Su smbolo lgico estndar y su tabla de funcionamiento se presentan a continuacin

.SELECTIO!'i

S $2 , st

L L .L L. l l L L H -L L H

-~ H 1:;. L H .L

.L. H H L H H H !... L

ii L L 8 !... H

.H !... :H H . H L

H. H l. H H H H H H

so

St S2

S3 M

Co

AC so A_1

B-j A.2 BZ A3

83

so

L

H. L H t. H L f'i L H L. H L H L H

6

.S

4

-:1

8

7

:2 ;..... K

23. r--..

,22. "'

21. .,.__

2o r:-.;

:19., "" 1K r--

M :::. l-l )GiC

PUNCTIONS :P-= .A .

---p =:AB.

F '" ; : : ."

-

Ci.rcuitos Aritmticos 1 2

La asociacin de AL U' s, para operar con ms bits , se puede hacer en serie (acarreo serie) o en paralelo (acarreo paralelo o acarreo rpido).

Para el primero, basta usar las entradas de acarreo anterior (Cl) y las salidas de --- ---= rr-.r-.\ p--- -~- 1 1~-- ,---~~~~e~,;~ -;~:la-- 1a d"" lor S''""'"'ar!nre"' acau cv ;:,e u e \\._.V), c.U..:l LI:- G se activa si la ALU genera un acarreo, o sea, si se produce una acarreo saliente (CO=l), independientemente de si hay o no un acarreo entrante (Cl=X).

> P se activa si la .

-

1

.1

J .

Circuitos Aritmticos

El siguiente diagrama es un circuito capaz de procesar 16 bits. Se trata de una ALU de 16 bits, con propagacin de acarreo en paralelo.

,.----------i Cl CPG

S[0-3] y MO Af0-15 i BJ2,:1..2. C;

---, (j :

..------__,4~- (:;Po ,.-------'>1" CGO

,----------=-"',_,CP1 ,-------...~:>..,CGI

,-----~.J:;P"j CP2 ..-----:-:' CG2

.------..,--"""1.. CP3 ~CG3

- ;li' _

- J 0 (n . : i~}G?P"-T -- r ~'i( (tr~ . j~f c:c> '-:

'--+-+-4--+---t~ '':'fi = f:Mj~ - :->1 J 1-f----"-p tlrt~'~:l~a~ ---t~j~---~r~ 1-+-: .. b ~-i . [2j p...-+-;

il--;1---+--"' , ci ''' p

11---C:I---4-"''' !. q 1-+-'~...- ~--- --s_ __ _,f~

COO-C01~rC0'2t----l-h

CG~""'---+-+-t----A otro CP~-'"' ~--1-ic---- CPG

(ii .. :y~l ,;; 1""-- (i>~~~i"%~(; ::r ;c .. .. : 1~1 -,;;o -1

F[0-15]

-

:-l)

~----- - --~~-- ~----------- --

J Una unidad aritmtico-lgka es un d~sposativo capaz de re:aiizar operaciones ~ matemcas y lgicas en el sistema binario. Esta unidad en concreto realiz3 un l "-ot-l da 1 ~ ""'-per--c;o,..,....,_s ~ .. ;tm, ...,;.l ..... ~~ v "'"'.:a.T~~ .:a.~~.:a.-- 'o' ~=~~s

'1. !.Cll .... V '-1 -G. j ,,..:;; .-...

-

.. H L H : H

A .H .ms A- . , A

CA + R): ~la~ -. r A o'1s Ul . '+ B) ma.~ : J .4. rnils s m:.5.,T AB in:$ (A +-ll ~:-1 + tr ms r A ms Acms: 1'. ,;!.JJ m:.'>-A. :wfu, l .4-B mi.c;..A ms .. ! :

,-\m~ t-

~

.-'--.

-

1

l

.l

) ,

l 2._

j '

.;( l L

~ _l_

~ : ,;.;.__

;l :l._

J,

_!._

l

:J,

,1__

_-1... 1 i

.A..

,,L_

::t,

) " ;l._

.~

..l.

>t X

~"' ~)"' ~l._

. /-'".!,

J . .A_

j j , ..,.r

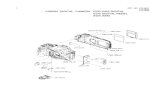

ELEMENTOS ARITMETICOS DIGITALES

l - S!\ /US1 N - - :viC 74181 P t - ZN 74181 E

10 -i3 - TL 7-181 N diagrama lgico

-1= 'V'

Unidad lgica aritmtica de 4 bits

2 F 7-US1 PC 3 F 93-!:1 PC 5 - DM 74181 N 6 -8 N 74181 N 9

11 FLH 401 12 -14 SF. C 4181 E 15 SW 74181 N

diagrama de cone:dn

,:. 1 1

SIMBOLOS LOGICOS OPERANDOS BAJO ACTIVO OPERANDOS ALTO ACTIVO

J1 ~ i/111

1 1 1

1 "

DESCR!PC!ON. Este dispositivo es una unidad lgica :utmetica IArithmetic Logic Unit) (ALU) paralela de alta velocidad de -t bits . Controlado por las cuatro B y A < B. LJ. tabla de funciones relaciona las opern..cioncs aritme:.ic:l.!i ejecutadas sin una entrada de acarreo. Un acarreo de ent.r"aeia aade. un uno a c:uia opcr.:1cin. De aqui que d cdigo LHHL genere A me~os D menos 1 (notacin de complemento .:1 :!.) sin una c:mrW::1 de J.C:l.ITeo v gen~n: .-\ mt:nos 8 cuando se apllqut: :1carreo. Como la resta se c::jt!cuta re!llmente mediante adicin complemcm.a.na (comoiemento a 11. . una SALlO A DE ACARREO signitic:J DEBE tBORROW): de aqui que sea generado un acarreo cuando

h

-

Entrad~s Salidas

Vi;:: c. P A.;, a

b =- )'"' \1 J.c, L u ; 1 .: .-;"7--o ]'' ''e-:- ~,,.) e:_:-.. Go;;. (Lt~ly .:).:::

( }111-""\h~...r\ . - -.

~ ~ ~ ~ ~ ~ ~ M ~ ~ ~ Entn; d2s Salidas .:~>c..._,

..

F:g:.:ra 4.23. Diag;ama de conexin de la ALU 74181 . -,

------------------------------------------------------------------------

Tabla 4.8. Funcione;gicas y operaciones aritmticas de la ALU 74181

L. L L L A A m;r:os 1 A L L L H AB A.B n1cno~ l AB L L H L A + B A.B menos 1 AB L L H H 1 Menos 1 (compl. a 21 O icero) L. H L L A ~ R A miL'i (A + H) A ms (A + ii} ms L H L H B A.n ms fA + B) ~\[) ms (A+ . B) .,ms ,1 _ H H L ASR A mcnus lJ menos A menos f

. . ~ .

' L H H H A + B A + B V\ + B) ms l ; L L L i \JJ A IU$ (A. + B) A JllS (A + B) ffillS 1 H L L H A EB B .4 ms B A m ~ B mas. l. ."'"' H L H L B \fl ms (A + B! Aff ms (A .. B) ms 1 H L .H H A + B A + B (A + B) m s f H 1-l L L o .A ms A i\ ms A. m:is 1 H H L H 1\B AB ms A AB ms A mm; l H H H L AB A.ii mils A All ms A ms H H H H A A A mas !

. EL NIVEL ACTIVO DE LOS OPERA.l"'DOS ES BAJO Y LAS SALIDAS TAMBIEN OBEDECEN A .NIVEL BAJO.

~~.

:....--...

._._ . .--...

-

1

1 ~

:1

.~

- J.:

J

)fj'ffl.LISIS CJYF.t: CO:

U6

-v :' . .,.,._ .

x . ~ :x .. _ : x.- x :_x :: _x :.-::c xxxxo 1 XX X X . 1. 1. X X X : o :i J

1 r .. L . :

. . < .. . .

. j . . l

.: ,~ . . . . . ..

. . .

so

S

GS

.-:"'-v "( x: V V ~~ .r

l X O. . l . J . :': . .......... . . : t.: .:'-'

\.1"': ' X , ., ,y - 7{ ------~ /\.' ' A "' X X V .y . X X _ ... .,._ .... ~-

-..,;- \~ X X ~( o 1""-' v ~-( V X ll .:"':\...

-"-

X .\. X (} L .-x _;;lo. o 1. l X ( ) ,. l i .l. o , . l . L

,. \

..'-.

... ,.

./\. o () ! 1 1

l l l

1.: j t

I 1,

1 l l l . l l

! . ! .1 . 1 .. 1 l 1 , .;.

1 1

r T. l J l 1 1 1

. . ( ::- . _:. :. -

1

,. l

l , 1 L

( l l : l l

l --- ~ :

.. ! . :

l 1 ,.

l 1 1 1

-,;. :' :.- . . .: .

. . .. -.~ : .. . ' : - :~-

-

) ( (

\ .. (

.. (

-~ .

-,(

-} -

,( :.~ --:(

-(l,,-(:

. --:~ ( -( ( _: ( ( _(;.~-::}.: ( _) ~_. :~-:l::.i ll!:) l

l o

.Id ni

[i] UJ o []

fiJ O LJ [J

O ID

O O

0

00

0

A

L

ro

dificad

or de

prio

ridad

y an

tirrebo

te Conecta

r con

A

e

',

~ .. ~o

-

1 ~

1 ------

. , .-..

:1 ~

:i .. ...

DECEI\JI\S UNIDADES

CUL ES EL NMERO MXlMO REPRESENTABLE?. COMPROBAR LOS VAlORES DE Y7 E Y3 PAt~A CUALQUIER COMBINACiN BDNAR!A DE ENTRADA. QU VALOR TIENEN?.

;.,., .. {

-

EL DECOOIFlCADOR 74138. MONTAR LOS ClRCUITOS DE LA FIGURA Y VERlFJCAR SU FUNCIONAMIENTO. ESCRiBIR LA FUNCiN LGICA IMPLEMENTADA POR EL SEGUNDO ESQUEMA_ VERiFiCAR LA CODiFiCACIN DEL TERCER ESQUEMA Y EXPLICAR SU FUNCJONr\MIENTO.

... .

- ~

;?:..: . ~

.. ~

' ;/: ,:;-;....

-

J

\ A

)',

U 7 44 7. CJYECCXDI'FI c;ICJXJ

-

5lf V L 'IIP L ~XO 1( 74151 1#i9S 3 2 'HAALf%''#WstfM9\ ;usa WWM 1 H

ESTUDIO DE MULTJPLEXORES. EL SELECTOR DE TRES BIT 74151. MONTAR EL CIRCUITO DE LA FIGURA CON PROTEUS , COLGAR DISTlNT AS

FRECUENCIAS DE ENTRADA PARA LOS GENERADORES 1 ... 8 . QU OCURRE CUANDO SE COLOCA LA COMBINACIN BINARIO 111 EN LAS ENTRADAS DE CONTROL?. QU FUNCIN REAL!ZAN LAS ENTRADAS EN Y OE?~

MODIF~CAR EL ClRCU1TO ANTERIOR PARA OBTENER LAS SIGUIENTES FUNClNES LGICA EN LA SALIDA Q. .

\

Q= A'B 'C' + AB'C' + ABC + A'BC

Q=A'B'C'D + A'B~CD'+ A'B'CD + A'EC'D'+ A'BCD + AB'CD + ABC'D + ABCD

3

i ; i

5

U1

SELECTOR 3

R? 330

Di LED-GREB

R1 . ' . : :

330

. .

.. ---..

.._

. . ...-...

-- ...--....

i ::~ : :e-:

.. ,....-....,

. '"'

;:;:; _.... -.. -. ;

-

1 ~

_j

_)

.. ~

EJEMPLO DE FUNCIONAMIENTO DE U~l DATO DE CUATRO BIT MUL TlPLEXADO. MONTAR EL CIRCUITO DE LA FiGURA Y COMPROBAR QUE SEGN LA POSiCIN DE

U15 SE INTRODUCE UN DATO U OTRO EN LE DISPLAY. S SE REAL!ZA LO E..XPUESTO ANTERIORMENTE CON VELOCIAD DE UNAS 25 VECES POR SEGUNDO NO SE APRECIAR EL PARPADEO. SXPUCAR EL FUNCIONAMIENTO.

U1frA

,-

-

P.L 9tlVL'IIPLCEXCYJ{ 74158

REALIZAR Y COMPROBAR EL FUNCIONAMIENTO DEL CIRCUITO REPRESENTADO. COLOCAR EL GENERADOR DE SEAL EN CLOK POR 2HZ. QU ES LO QUE SE OBSERVA EN LOS DIPLAY?. CU..L ES !_.,. FUNCIN DE LA PAT!LLA ~DEL 74153?. SUBIR LA FRECUENClA DEL RELOJ A30 HZ. :QU SUCEDE AHORA?.

U2 UtA

~ . . .

U1:E 74HC!l4

: _,-...

.-....

~

.. _,--...

_ ... ,

.: ...-....

. ' ;_

. ~

"/'

..-.. _-;----..

-~- . ..-:-

. . ~

-

.:d._

. l

;.1:

* dl!FW NSS.HIB * i HHN!

MONTAR LOS C!RCU!TOS REPRESENTADOS Y CONTESTAR: 1. PORQU ACTA COMO DEMUL TlPLExOR?.

IWIJ K$ ?bbW U

2 . . EXPLICAR EL FUNCIONAMIENTO DEL DECODIFiCADORJDEMUL TiPLEXOR.

U2(E1)

'------!"~ ... ; ..

74154

-

~=rJ ~ EL 7485, COMPARADOR DE CUATRO BIT. RELLENAR LA TABLA ADJUNTA.

A UNl[)P.DES A DECEf\JAS

8 Uf'.llDADES B DECENI\S

.. ;'',' :~:-~ .= . ~~;'tf.:,~~-, :.~: f--'--"---"--'-'---t--'----'-------+------------r: :.;-, ~''Y' . , .. ,.

r--------t--------+--------------1 : .. ~~~{:~:.";-_~~~:- ~- >~ --~ . . ~-~-: . . ~ ..

A

-

DETECTORES DE PARIDAD PAR E IMPAR EL 742LS80. EfECTUAR UNA TABLA CON DIEZ NMEROS BINARiOS ALEATORIOS Y NOTlFlCAR SU BIT DE PARlDAD.

PARIDAD PAR

. PP.J~!DAD I~J1PAR

MONTAR EL CIRCUITO DE LA FiGURA Y RELLENAR LA TABLA ADJUNTA.

U4 A ~)-~---'-. 8 f'!iH :i~-----rt--'--~.

Ci

SUIV~DOR CONPLETO SUi\11A

'. :. .

U2A

~ , ..

- SV5rf)~fD()

-

' ,.... .:: -

1

----

L

J

-----

i /--..

MONTAR LOS ClRCU!TOS DE LA fiGURA. Y COMPROBAR L~ SUMA Bl~JAR!A PARA DISTINTOS VALORESDEL NA Y DEL N8. 'EL RESULTADO ES EN HEXADECIMAL

r:

RESUL T.AOO C:N HEXADEC1l'v1AL >>

CARI~Y ~l._ ~ t~~~~~--- . :-: (~~~1~~9~~~jQ~Y.1~ __ ---;~A~~

- CO~c.RSO

-

j - - -- - --

~\

EL CIRCUITO DE LA FIGURA ES UN SUMASOR-RESTADOR DE CUATRO BlT. PAP~ QU SON LAS PUERTAS EXCLUSIVE OR?: REALIZAR LAS OPERACIONES DE LA TABLA ADJUNTA.

A3 A2 A1 AO (N A) 83 82 81 80 (N 8) SUMJRES RESULTADO

1 ..L.._ .

--".

1

1 o 1 1

o 1 o o 1 1 o o o 1 o o

1 ' 1 o o 1 ~ tLf o o o 1 o t4 1 1 o o 1 IZ.. 1 1 1 1 o 1-6'

U4 74283

-

-::-:- ...

SUMADOR BCD. REALIZAR EL ClRCU~TO DE LA FIGURA Y COMPROBAR QUE EL RESULTADO ES EN BCD. CUL ES EL NMERO M~"'CIMO REPRESENTADO EN EL RESULTADO?. COMPROBAR LA SUMA DE TODAS LAS COMBINACIONES POSlBLES DE DOS NMEROS EN SISTEMA BCD.

, U3:A

711)4

. :...~

. - .

. -. ...............

~ ' .. :._~

. . . .i'-.

. ,.,.-

:. .. :...-...

-

J.~---

1 .....__

~ ).__

;( )_ J._

REAUZAR EL CIRCUITO RESTADOR BCD. TENER EN CUENTA QUE SOLO PUEDEN ENTRAR NMEROS COMPRENDIDOS DESDE EL CERO HASTA EL NUEVE Y REALIZAR VARIAS OPERACIO"NES DE RESTA .

U2

.)_ ~f B !]~----, ..

A.

UJvfl.E\tOOOA ME/E U3.:A

-

--.... SV5tf)!CJJO

o

o :z:

XRJ

U 1M

. unA 74rn

U2

U14:A

. ;-

.,,__..._

..: . . ........_

-~~

.

.... -..

t:::- ..........._ .:.

.;. . ,........., ~-,

. .~

~ ::---

-:: -,.-. ..

-

w~~~~~Ja&Uf2**~ EL CIRCUITO REPRESENTADO EN LA FlGURA ES UNA UNIDAD ARHMTiCO LGICA.

LSH Y RSH . DESPLAZi!.. N9A LAS VECES QUE INDIQUE NB NEGA Y N!EGB SE UTILIZA PARA EL SIGNO.

-

Montar e! circuito de la figura y rellenar la tabla adjunta. Comprobar los resultados obtenidos. El circuito de puede realizar con el Wordbench o con el Circuit Maiker2000.

1-oJ

1-o

1-o

1-o

1-

!SJ !-o

1-o

F .} r

. DISPl 11 12 13 14 o aaa _

4321

....

: _;.-..

.. .-.......

~~- . -..: .:-. - .. . ---...

:~:~ ... ~

.. .

-~

-

1 ----._

REAUZAR LA TABLA P.A.RA LA ALU 74~81. ESPEClFlCAR LA OPERACIN REALIZADA AS COMO EL RESULTADO OBTENIDO, COMPARARLO Y VERIFICARLO.

l g ~ rs3-s2-s-~f) n=uc.ia~rif. :-c"N ;cA.1u~y-- -N i.. --- ~-N"o_s __ - - --: -F'ERJi.c-io.~TT RE"scr:- : l_ .--o--a--a-a --- ~-- ; :1- ---- - - ~~x __ -: ______ ~ ___ : __ ; 1-o1o - - - - - ---~----- (~x-- - :-- -- - --- .. - - :~--------------- -----~--~~--.L -- a-a a- 1 T ~:r - .. --x ----- .. : 11oo ... ------ - ao11---- :-- ------ --~~~~---------~ (1a~-t-~r- - --~o _ -~,~- ~-o-----~---r-ffo1--- - -:-0191 - -- -:--- : _

~ fLL~ ~E:E~P--~~~~~~~--- =HJ~E --~~~IL> ~-}~~~ ~-~::;-~== ;___ 1 1 1 o o =n : o : 0111 . 1 xxxx i i

t . . , .. .. . .. , . . .. .. , ~ ,. . . . . . . L..... . . . .. .. , . ~ . . . , . . . . . . , .. . . . . .. . . . .. . . . .. ' . . . . . . ... . .. ...... ,; ' ....... . h ,,. , ,

.L --1~~~--o-~--r;;-.,~--- --_ --~ c--.x.- . .. .. . rxx-xx----- ~ . - ;-------) ___ -_-_--_-

.L : :J-1~--o--~r~;1-----___ -__ -~~f-~. ~---~-- __ -__ -__ ~~(-fo-ta - ---~~f-Df.t~--- -__ ~~---- :-~--~----_ -~~e--__ ----- ~-~~~ -~ L}J ___ 1~_f_.L_~~~_c--~~ - nL. 1 .. .. ~>:.1~~1"-- ._:.J~ -- -- -- ,~ --1'~-__ -=_c.c_:~.:=_:_

SELECCIN OPERACIN

L L L L L L L H L L H L L L H H L H L L L H L H L H H L L H H H H L L L H L L H H L H L H L H H H H L L H H L .H H H H L H H H H

FUNClN LGlCA OPERACIN ARITMTICA M=O M=1 CARRY=O CARRY=1

-

A A menos l. A -

AB AB menos 1 AB -

-A+B AB menos 1 AB 1 Menos 1 (compl. a 2) O (cero)

A+B A ms (A + B) A ms (A + B) ms 1 -

B AB ms (A + B) . A 8 ms (A + B) ms 1 AEBB A meDos B menos 1 A menos B

--A+B A+B (A + B) ms 1

-

AB A ms (A + B) A ms (A + B) ms 1 AEBB : A ms B A ms B m~ l

B AB ms (A. + B) AB ms (A + B) ms 1 A+B A..+B (A + B) ms 1

o A ms A A mili; .4 ms 1 -

AB AB ms A AB ms A. ms l. - AB ms A ms 1 AB AB ms A

A A A ms 1

-

PROBLEl\-LL\S DE CIRCUITOS CO!\:!Bl!"'l"ACIONALES INTEGRADOS

-Sistemas digitales- 1 lnformtica de Sistemas (2003-2004)

1 ") Sea un sistema digital que dispone de 16 lne:JS de pt:ticin de servicip activas en baja. Disear un circuito que nos muestre a travs de dos displays el nmero de la lb~n. de petic.~n de servicio de mayor prioridad activa en cada instante. Si no hay ninguna activa, nb, mostrar 'nada. Hacer el diseo con dos codificadores de prioridad '148, dos conversores de cqigo '48 y d~s displays . Utilizar las puertas que sean necesarias. \. .

2) Disear un multiplexor de 16 canales a partir de dos multiplexores '15 l. Emplear las puertas que sean necesarias.

3) Sea la funcin lgica de cuatro variables: . f(a, b,c, d) = I, (0,2,4,5,6,11,12,14)

Implementarla con un multiplexor' 151 y un inversor

4)Disei3.ar uu.circuito que realice la suma del nmero A de cuatro bits (a3 a2 a1 ao) con el mayor de los dos nmeros B (bJ b2 b t bu) y e (cJ c2 C Co) . Los tres nmeros estan codificados en el sistema binario natural. Si los nmeros By C son iguales, el resultado ha de ser igual al nmero A. Utilizar para el montaje los circuitos combinacionales integrados que s::an necesarios.

SO) Se dispone de dos circuitos integrados. El primero de ellos contiene dos sumadores completos de 2 bits, y el segundo es un multiplexor '151. Utilizando los 2 circuitos anteriores y los inversores que se precisen, disear un circuito capaz de detectar la presencia de 3 y slo 3 bits a" 1 ", en palabras de 6 bits en paralelo.

6) Disear un sumador aritmtico en cdigo BCD para nmeros positivos de una cifra a partir de dos sumadores integrados '83 y las puertas que sean necesarias. Generalizarlo para sumar nmeros BCD de ms de u\:ifra.

7) Disear: a) Un circuito sumador-restador de 3 bits y signo. Utilizar para ello un circuito sumador '83

y las puertas X-OR que sean necesarias. b) Un detector de rebasamiento para el sumador-restador del apartado anterior. e) Un sumador-restador de 7 bits y signo con detector de rebasamiento.

8) Se dispone de dos termmetro digitales A y B. Cada uno de ellos entrega una seal binaria de 4 bits. Los dus termmetros no siempre dan la misma temperatura., por lo gue interesa disear un circuito que realice 4 funciones segn las seales de control G1 y GoJ:

G1 Go FUNCIN o 'O Media redondeada por defecto o 1 Temperatura de A 1 o Temperatura de B 1 . 1 !Media redondeada por exceso

Se dispone para el diseo de uri sumador integrado '83, 2 multiplexores '157 .y las puertas necesarias.

El resultado debe aparecer en un display (unidades) y en un led las decenas . Realizar este circuito utilizando otro sumador '83 , un conversor de cdigo 'LlS, el display, elled y el nmero mnimo de puertas lgicas necesarias.

. ~ ,.,....-.,

\ ... ;..

.,~

:------

" "?""---

...--......

-: .~_ ;._

-

) _,____

)

L_

) -~

.l

1 ~,

_J,

; . .-.

ll_

.JZ

l. _.--.

11

Se comparan dos nmeros de ocho bit cada uno, el n-mero 8 (b7,b6,b5,b4,b3 ,b2.b1 ,bO) con el nmero e (c7,c5 c5,c4,c3,c2,C1 ,cO). S B > C entnces se suman los cuatro bit de menos peso de 8 con el nmero A de cuatro bit y e! resultado aparece en un display. S B