Darek Sugier ''Dzienniki Jessego'' (złożone, złamane, gotowe do druku)

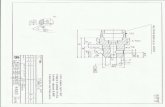

JS Układy bipolarne1 1 JS UCiSW1Układy Cyfrowe i Systemy Wbudowane 1 II. CYFROWEUKŁADYSCALONE dr...

Transcript of JS Układy bipolarne1 1 JS UCiSW1Układy Cyfrowe i Systemy Wbudowane 1 II. CYFROWEUKŁADYSCALONE dr...

1

1

JS UCiSW1

Układy Cyfrowe i Systemy Wbudowane 1

II. CYFROWE UKŁADY SCALONE

dr inż. Jarosław [email protected]

W-4/K-9 pok. 227 C-3

2

JS UCiSW1

+UCC

A

B

A·B A

B A+B

+UCC

A

A

Logika diodowo-tranzystorowa

Sygnały napięciowe w logice dodatniej:

• 0 log. ⇔ napięcie ≈ GND

• 1 log. ⇔ napięcie ≈ +UCC

Układy bipolarne

3

JS UCiSW1

+UCC

B

A·B

A

+UCC

+5V

B A·B

A T1 T2

T3

T4

4k

1k6

130

1k

Transistor – Transistor Logic (TTL):

NAND DTL:

4

JS UCiSW1

Tranzystor MOS (Metal-Oxide-Semiconductor)Structure:

n+

S G D

p-substrate

GND

n+

Induced channel:

Resistive (linear) operation: Saturation:

n+

S G D

p-substrate

GND

GND

VGS > VT VDS = 0

n+

n-channel

n+

S G D

p-substrate

GND

GND

VGS > VT VDS < VGS – VT

n+ n+

S G D

p-substrate

GND

GND

VGS > VT VDS > VGS – VT

n+

Układy unipolarne

5

JS UCiSW1

Logika MOS

G

S

D

NEMOS

(z kanałem wzbogacanym,

Enhanced, norm. OFF)

G

S

D

NDMOS

(z kanałem zubożanym,

Depleted, norm. ON)

SRCH

D

G

A·B

+VDD

A

RL

B

A+B

+VDD

B

RL

A

+VDD

A

A

RL

• Uproszczony dwustanowy model rezystancyjny:

RL >> RCH

6

JS UCiSW1

Bramki CMOS (Complementary MOS)

P(E)MOS – ON dla WE = L N(E)MOS – ON dla WE = H

+VDD

A A

+VDD

A A

2

7

JS UCiSW1

+VDD

A·B

A

B

+VDD

A+B

A

B

8

JS UCiSW1

),,()(

),,()(

cbaFcbafF

cbaFcbacbacbafF

NMOSDN

PMOSUP

=+==

=+=++=+==

Uogólnienie: bramki AOI (And–Or–Invert) / OAI (Or–And–Invert)

+VDD

(a+b)·c

a

b

c

a b

c

• 1 BR (bramka równoważna) = 1 NAND/NOR 2WE = 4 tranzystory / 2 pary kompl.

• Tu: 6 tranzystorów (3 pary komplementarne) = 1.5 BR

1.5 BR

)()()1Np. OAIcbaf +=

9

JS UCiSW1

( )),,(

),,(

cbaFbcafF

cbaFcbabcabcafF

NMOSDN

PMOSUP

=+==

=+=⋅=+==

• Podobnie: 6 tranzystorów (3 pary komplementarne) = 1.5 BR

1.5 BR

+VDD

a+bc

b c

a

b

c

a

)()2Np. AOIbcaf +=

10

JS UCiSW1

IC Fabrication Process

(C) Taiwan Semiconductor Manufacturing Co., Ltd.J. Rabaey, A. Chandrakasan, B. Nikolic: Digital integrated circuits

(C) Taiwan Semiconductor Manufacturing Co., Ltd.

11

JS UCiSW1

Full custom ASIC

• E.g. Cadence: Virtuoso

• Synopsys: Custom Compiler / Design Compiler

• Mentor (Siemens group): Calibre12

JS UCiSW1

3-input NAND cell

Standard Cell Libraries

• Np. biblioteka sxlib oprogr. Alliance: (Laboratoire d'Informatique de Paris 6)

Design mapped to cells| Placement| Power routing| Clock tree synthesis

From a tutorial by

C. Batten, Cornell Univ.

| Final design (fully routed, critical path highlited)

• Np. Synopsys Educational 90nm Standard-Cell Libraries i IC Compiler:

3

13

JS UCiSW1

Gate Arrays

Lata 80., 90. …

• S-MOS Systems, SLA6140:

• NEC, Hitachi, Fujitsu…

• Atmel: ATL25 Gate Array ASIC ATL25 Embedded Array ASIC

14

JS UCiSW1

Programmable Logic Devices (PLD):

Complex PLD:

15

JS UCiSW1

Field Programmable Gate Arrays (FPGA)

16

JS UCiSW1Koszty stałeFPGA G.A. S.C.

Training (days) 2 5 5

$400 / day $800 $2 000 $2 000

Workstation $10 000 $10 000 $10 000

Software $1 000 $20 000 $40 000

Design (10k gates)

gates / day 500 200 200

days 20 50 50

$400 / day $8 000 $20 000 $20 000

Production test design 0 5 days 5 days

0 $2 000 $2 000

NRE 0 $30 000 $70 000

masks 0 (3÷4) $10 000 (15+)$50 000

simulation 0 $10 000 $10 000

test 0 $10 000 $10 000

Second source (5days) (5days) (5days)

(projekt „awaryjny”) $2 000 $2 000 $2 000

Total $21 800 $86 000 $146 000

Michael J.S. Smith, ASIC

17

JS UCiSW1Koszty jednostkowe

FPGA G.A. S.C. unit

Wafer size 6 6 6 inches

Wafer cost 1 400 1 300 1 500 $

Design size 10k 10k 10k gates

Density 10k 20k 25k gates/cm2

Utilization 60% 85% 100%

Die size 1.67 0.59 0.40 cm2

Die / wafer 88 248 365

Defect density 1.10 0.90 1.00 cm-2

Yield 65% 72% 80%

Die cost 25 7 5 $

Profit margin 60% 45% 50%

Part cost 39 10 8 $

Price / gate 0.39 0.10 0.08 cents

Michael J.S. Smith, ASIC 18

JS UCiSW1

Wyrównanie:

FPGA vs. Gate Array ≈ 2.000 szt.

Gate Array vs. Standard Cells ≈ 30.000 szt.

10 000

100 000

1 000 000

10 100 1 000 10 000 100 000

SC GA FPGA

[Total $]

[Volume]

Koszt [$] FPGA G.A. S.C.

stały 21 800 86 000 146 000

jednostkowy 39 10 8

Koszt całkowity

4

19

JS UCiSW1

„Time to market” delay

Michael J.S. Smith, ASIC

20

JS UCiSW1

Bezpieczniki (Fuses)

21

JS UCiSW1

Antybezpieczniki

Actel: PLICE (Programmable Low-Impedance Circuit Element)

QuickLogic: ViaLink

Michael J.S. Smith, ASIC

22

JS UCiSW1

EPROM

n+ Source n+ Drain

P-Type Silicon

VPP

VD < VPP

floating gate access gate

thin gate oxide

FAMOS = Floating-gate Avalanche-injection MOS

E2PROM

n+ Source n+ Drain

FLOTOX = FLOating – gate Thin OXide trans.

23

JS UCiSW1

Początki: pamięci PROM

D3 D2 D1 D0

0

1

2

255

DE

KO

DE

R

A0

A1

A2

A7

. .

.

.

.

.

.

.

.

.

.

.

.

.

.

24

JS UCiSW1

+VDD

I1

IN

T1

+VDD

TK

+VDD

F1

+VDD

FM

WE

WY

Matryca

AND

Matryca

OR

Matryca PLD

5

25

JS UCiSW1

. . . . . .

. . .

T1 TK

połączenia progr.

połączenia progr.

I1 I2 IN . . .

. . . . . .

. . .

F1 FM

. . . . . .

. . .

T1 TK

połączenia progr.

połączenia progr.

I1 I2 IN . . .

. . .

F1

. . .

FM

. . .

I1

IN

TK

FM

T1 T2 T3

F1

. . .

F2 . . .

26

JS UCiSW1

PAL(Programmable

Array Logic)

PLE(Programmable Logic Element)

PLA(Programmable

Logic Array)

Matr. AND: Progr. Const. Progr.

Matr. OR: Const. Progr. Progr.

27

JS UCiSW1

T0

F0

F1

F2

F3

T1 T2 T7

I0

I1

I2

. . .

Układy PLE

Np. 8x4:

⇔⇔⇔⇔

⇔⇔⇔⇔

O0

O1

O2

O3

OE (output enable)

IN OUT

OE

OE = 1 OUT = IN (0/1)

OE = 0 OUT = Z (HighZ)

28

JS UCiSW1

PAL16L8 0 3 4 7 8 11 12 15 16 19 20 23 24 27 28 31

0

7

0 3 4 7 8 1 1 1 2 1 5 1 6 19 20 23 24 27 28 31

8

1 5

16

2 3

24

3 1

3 2

3 9

4 0

4 7

4 8

5 5

5 6

6 3

I0

I1

I3

I4

I5

I6

I7

I8

I2

O8

I/ O7

I / O6

I/O 5

I/O 4

I/O3

I / O2

O1

11 I9

N D

VC C1

2

3

4

5

6

7

8

9

12

13

14

16

17

18

19

1 5

20

16 L8-5 ( -4)

1 0

16 L 8

29

JS UCiSW1

0 3 4 7 8 11 12 1 5 1 6 19 20 2 3 24 27 28 3 1

0

7

8

1 5

16

2 3

24

I 0

I1

I 3

I2

O8

I/ O 7

I / O6

VCC 1

2

3

4

1 7

1 8

1 9

2 0

16L8- 5 ( -4) 1 6 L 8

30

JS UCiSW1

PAL16R80 3 4 7 8 11 12 15 16 19 20 23 24 27 28 31

0

7

0 3 4 7 8 1 1 1 2 1 5 1 6 1 9 2 0 23 24 27 28 31

8

15

16

23

24

3 1

3 2

3 9

4 0

4 7

4 8

5 5

5 6

6 3

16R8-5 (-4)

2

3

4

5

6

7

8

9

1

18D Q

Q

19

17

16

15

14

13

12

11

O8

O7

O6

O5

O4

O3

O2

O1

OE

V

CLK

I1

I2

I3

I4

I5

I6

I7

I8

D Q

QV

D Q

QV

D Q

QV

D Q

QV

D Q

QV

D Q

QV

D Q

QV

G N D

VCC

1 0

20

16R8 ( 4)

6

31

JS UCiSW1

0 3 4 7 8 11 12 15 16 19 20 23 24 27 28 31

0

7

8

15

16

23

24

16R8-5 (-4)

2

3

4

1

18D Q

Q

19

17

16

O8

O7

O6

O5V

CLK

I1

I2

I3

D Q

QVD Q

D Q

QV

VCC20

16R8 ( 4)

32

JS UCiSW1

0

3

4

7

8

1 1 1 2

1 5

1 6

1 9

2 0

2 3

2 4

2 7

2 8

3 1

0

7

8

1 5

1 6

2 3

2 4

3 1

3 2

1 6 R 6 - 5 ( - 4 )

2

3

4

1

1 8 D

Q

Q

1 9

1 7

1 6

1 5

I / O 8

O 7

O 6

O 5

O

V

C L K

I 1

I 2

I 3

I 4

D

Q

Q V

D Q

Q V

D Q

V C C

5

2 0 1 6 R 6

33

JS UCiSW1 PALCE22V10 and PALCE22V10Z Families

0

1

9

SP

AR0 3 4 7 8 11 12 15 16 19 20 23 24 27 28 31 32 35 36 39 40 43

10

20

21

0 3 4 7 8 1 1 1 2 1 5 1 6 1 9 2 0 2 3 2 4 2 7 28 31 32 35 36 39 40 43

CLK/I0 1

(2)

2

(3)I1

3

(4)I2

4

( 5 )I3

5

( 6 )

I4

6

( 7 )

I5

7

( 9 )

I6

8

( 1 0 )

I7

9

( 1 1 )I8

1 0

( 1 2 )I9

1 1

( 1 3 )

I 1 0

1 2

( 1 4 )

G N D

24

(28) VCC

(16)

I1311

34

33

48

4 9

6 5

6 6

8 2

8 3

9 7

9 8

1 1 0

1 1 1

1 2 1

1 2 2

1 3 0

1 3 1

I/O923

(27)

8I/O22

(26)

I/O21

(25)7

I/O20

(24)

6

5I/O19

(23)

4I/O18

(21)

I/O17

(20)

3

I/O16

(19)

2

I/O15

(18)

1

I/O14

(17)

0

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

Q

Q

Q

Q

Q

Q

Q

Q

Q

Q

16564E-006

PALCE22V10

0

1

9

AR0 3 4 7 8 11 12 15 16 19 20 23 24 27 28 31 32 35 36 39 40 43

10

20

21

CLK/I0 1

(2)

2

(3)I1

3

(4)I2

4

( 5 )I3

24

(28) VCC

34

33

48

4 9

I/O923

(27)

8I/O22

(26)

I/O21

(25)7

I/O20

(24)

6

5I/O19

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D

SP

ARQ

0

1

1 0

1 1

0 0

0 1

D AR

1 0

1 1

Q

Q

Q

Q

34

JS UCiSW1

35

JS UCiSW1

Complex PLD

Glo

bal inte

rcon

ne

ct m

atr

ix

PA

L

I/O I/O I/O

MC

MC

MC

PA

L

I/O I/O I/O

MC

MC

MC

PA

L

I/O MC

MC

MC

I/O I/O

PA

L

I/O MC

MC

MC

I/O I/O

36

JS UCiSW1

Arch. XC9500XL

7

37

JS UCiSW1

Arch. XC9500XL

38

JS UCiSW1

39

JS UCiSW1

40

JS UCiSW1

41

JS UCiSW1

42

JS UCiSW1

VIN

8

43

JS UCiSW1

44

JS UCiSW1

Boundary scan logic:

Joint Test Action Group (JTAG) IEEE Std. 1149.1

45

JS UCiSW1

State diagram for the TAP controller