[IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications -...

Transcript of [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications -...

![Page 1: [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications - Calgary, Alta., Canada (30 June-2 July 2003)] The 3rd IEEE International Workshop on](https://reader035.fdocuments.pl/reader035/viewer/2022080422/5750a5461a28abcf0cb0bde5/html5/thumbnails/1.jpg)

A 52 GHz VCO with Low Phase Noise Implemented in

SiGe BiCMOS Technology

Lin Jia, Alper Cabuk, Jian-Guo Ma, Kiat Seng Yeo, Manh Anh DoRFIC Group, Center for Integrated Circuit & Systems (CICS)

Nanyang Technological University, [email protected]

Abstract

A fully integrated 52 GHz millimeter wave LC VCO

with –106 dBc/Hz phase noise at 600 kHz offset frequency

and 0.93 GHz tuning range is reported in the paper using

IBM BiCMOS-6HP technology. The output voltage swing

of the VCO is about 0.4 Vp-p for the complementary

cross-coupled topology with the buffer. A bipolar device

is used as the tail transistor to supply constant a current

to preserve the oscillation of the VCO. The parasitics due

to interconnect metals are extracted from the layouts, the

effects of those parasitics on the VCO’s performance are

investigated. Based on the analyses, the optimized layout

of the complementary VCO is obtained, the pre-layout

and the post-layout simulations are compared and

presented in this paper.

1. Introduction

High frequency and low phase noise oscillators are

key components in achieving high performance and low

cost millimeter wave (MMW) applications such as

wireless communication systems and automotive radar

systems. Several monolithic MMW voltage controlled

oscillators (VCOs) have been reported using HEMT [1],

InP-based HBT [2] and CMOS technologies [3].

However, the phase noise is limited by the high intrinsic

1/f noise presented in HEMTs, the small tuning range as

well as high power consumption in InP based HBTs, and

the high substrate loss in CMOS technology [4]-[6]. The

SiGe BiCMOS is chosen in this paper because of its

impressive high frequency performance at both device

and circuit levels [7]. Furthermore, substrates used in

SiGe BiCMOS processes typically have a medium

receptivity of 10-20 -cm resulting in high quality

inductors compared to those made on the standard CMOS

processes. The thick metal layer that comes with the state-

of-the art SiGe technologies also improves the inductor

performance. This makes SiGe BiCMOS an attractive

alternative for the high frequency VCO design, where

both high-speed active and high-Q passive devices are

needed. The IBM BiCMOS-6HP technology has been

selected in our design.

In this paper, a microwave monolithic LC VCO using

the IBM BiCMOS-6HP technology is presented. The

MMIC VCO has been designed and post-layout

simulated. The oscillation frequency is as high as 51.8

GHz with a tuning range of 0.93 GHz, and a peak-to-peak

buffer output voltage of 0.4V. The phase noise is –89.5

dBc/Hz at 100 kHz offset frequency and –106 dBc/Hz at

600 kHz offset frequency. To the authors’ knowledge,

this is the highest oscillation frequency achieved for a

fundamental-mode VCO in an IBM BiCMOS-6HP

process with fT = 45 GHz. The phase noise performance

is almost 10 dBc/Hz better than that of a recently reported

50 GHz CMOS VCO [3].

2. LC VCO topology design strategy

The circuit diagram is shown in Fig. 1(a). A fully

integrated complementary cross-coupled configuration is

chosen because of the following advantages:

The oscillation amplitude of this structure is

approximately twice the amplitude of the nMOS-only

structure due to the pMOS cross coupled pair [8]-[11].

The differential operation of this topology makes the rise-

time and fall-time symmetrically during the oscillation

and results in a reduced 1/f noise upconversion [11] and

an improved phase noise performance for a given tail

current.

The bipolar tail transistor used in this topology improves

the phase noise performance of the VCO because the flick

noise of the bipolar is 10dB lower than that of MOS

transistor [13].

As shown in Fig. 1(b), a differential LC VCO can be

represented as a parallel RLC circuit. In this circuit, the

conductance, Gtank, represents the inductor and varactor

losses. Gactive is the effective negative conductance of the

active devices in the nMOS (Mn1 and Mn2) and the pMOS

(Mp1 and Mp2) cross-coupled pairs in order to compensate

for the loss of the tank. The cross-coupled VCO operates

as a switch: Firstly, it is noted that the oscillator forces

VGD of the nMOS transistors to be equal in the

magnitudes but with opposite signs to generate a

differential voltage across the resonator. At the zero

differential voltage, shown in Fig. 1 (c), both switching

nMOS transistors (Mn1 and Mn2) are in saturation region,

and they form a small-signal negative resistance that

induces the startup of the oscillation. As the differential

oscillation voltage crosses Vth, VGD of one nMOS ( Mn1)

exceeds +Vth, forcing it into the triode region; VGD of the

Proceedings of The 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications ISBN 0-7695-1929-6/03 $17.00 © 2003 IEEE

![Page 2: [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications - Calgary, Alta., Canada (30 June-2 July 2003)] The 3rd IEEE International Workshop on](https://reader035.fdocuments.pl/reader035/viewer/2022080422/5750a5461a28abcf0cb0bde5/html5/thumbnails/2.jpg)

other nMOS (Mn2) falls below +Vth, driving the device

into the deeper saturation, and then Mn2 turns off.

Mp1 Mp2

Mn1 Mn2

MosVar1 MosVar2

Inductor

Vdd

Vcontrol

Ibase

Mn4Mn3

Output1 Output2

R2R1

(a)

L C

Gta

nk

Gacti

ve

Saturation area

Differential Zero

(b) (c)

Similarly, as the falling differential oscillation voltage is

smaller than –Vth, VGD of one pMOS (Mp1) exceeds –Vth,

forcing it into the triode region, VGD of the other pMOS

(Mp2) forces this transistor into deeper saturation, and

then Mp2 turns off. Thus, the complementary LC VCO

operates when both nMOS and pMOS pairs are all in

saturation region firstly, then one nMOS and one pMOS

are at the off states, while other nMOS and pMOS are at

the triode region. Such switching process is periodical

throughout the operation of the VCO. The oscillation

frequency is LC

f2

10 . In order to sustain the

oscillation, the formula |Gactive| Gtank must be satisfied.

However, Gactive and Gtank are two main noise sources

during the operation of the VCO, here,

2

mpmn

active

GGG , Gmn and Gmp are the

transconductance of the nMOS and pMOS respectively,

thus optimized active devices can improve the

performance of the VCO phase noise.

effR

G1

tank , Reff

is the effective resistance which includes the tank parallel

resistor, Rp, the series parasitic resistor, Rl, of the inductor

and the series parasitic resistor, Rc, of the capacitor at the

oscillation frequency, 0f , and hence Reff can be expressed

as [7]:

2

0 )(

1

CRRRR

p

lceff (1)

High-Q inductor and the varactor are the most critical

elements in a VCO design when a low phase noise is

desired. However, due to the skin effect at microwave

frequencies, the inductor Q value and the self-resonation

frequency are reduced, thus, the targeted oscillation

frequency are shifted. In order to address these issues, the

IBM BiCMOS-6HP process is chosen in our design for

the following advantages [8]:

Its high resistive substrate reduces the Eddy

currents and the thick metallization minimizes

the skin effect. These features make it possible to

obtain Q values of around 20 for inductors at the

operation frequency.

The IBM BiCMOS-6HP process offers

transmission line inductors with deep trench

isolation further improving the inductor Q

values, and hence oscillation above 51 GHz with

low phase noise is feasible.

The Bipolar tail transistor schematized in Fig. 1 (a) can

be realized together with the CMOS circuit in this SiGe

BiCMOS process.

3. SiGe integrated inductor line and

mosvaractor

3.1. Inductor line

One of the key components for designing a low phase

noise oscillator is the high Q inductor. Unlike capacitors,

inductors are not readily available in a standard CMOS

technology. As a result, some design techniques have to

be used, that usually limit the performance of an inductor.

The active inductors could be very advantageous in high

frequency operation for VCO. However, the noise

generated by the active elements requires the use of an

excessive amount of power [15]. Recently, an inductor of

a folded bondwire has been proven to have low series

resistance and it is readily available in any IC technology.

The semiconductor industry is still hesitant to use this

technique because manufacturers cannot guarantee the

repeatability of the bonding process. Currently, various

spiral-shaped inductors have been designed and

fabricated on the silicon substrate using one or more

metal interconnection levels. However, the inductor Q

Fig. 1. (a) The topology of the complementary LC VCO

(b) Differential equivalent circuit

(c) Output voltage of oscillator

Proceedings of The 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications ISBN 0-7695-1929-6/03 $17.00 © 2003 IEEE

![Page 3: [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications - Calgary, Alta., Canada (30 June-2 July 2003)] The 3rd IEEE International Workshop on](https://reader035.fdocuments.pl/reader035/viewer/2022080422/5750a5461a28abcf0cb0bde5/html5/thumbnails/3.jpg)

value is limited by the series resistance of the metal traces

and the substrate loss.

For frequency around 50GHz, Microstrip line

inductors are used such as they can provide the required

low inductances at high Q value, The IBM BICMOS-6HP

technology offers a set of microstrip line inductors with

an additional deep trench layer underneath the inductor

lines to enhance the Q values further.

Fig. 2 shows L and Q values of the microstrip line

inductor and the spiral inductor versus frequency, both

aiming for a 50 pH inductance at 55 GHz operation

frequency. A simple microstrip line inductor exhibits a

50.6 pH inductance and a Q value of 28. Unfortunately,

the smallest spiral inductor available in the IBM library is

160 pH. The 50 pH inductance can be obtained by

paralleling three 160 pH spiral inductors, but the space is

5 times bigger than that of the microstrip line inductor

and the Q value is only 7. The feasibility of high

frequency and low phase noise LC VCO will be based on

the superiority of the microstrip line inductors.

3.2. Mosvaractor

Voltage-controlled capacitors, also called varactors,

are the key components in a VCO. A varactor diode,

which is formed by an intrinsic pedestal npn collector–

base diode, is offered by IBM BiCMOS-6HP technology.

The Cmax/Cmin ratio is about 12 for this structure, but the

varactor Q is less than 8 at 55 GHz.

The IBM BiCMOS-6HP process also offers an nMOS

varactor with a higher Q value, which is suitable for

realizing small capacitances for the high frequency VCO.

The capacitance and Q are shown in Fig. 3 at the

operation frequency of 55 GHz. A nMOS varactor

(MosVaractor) uses a thin oxide NFET in an N-well with

the N+ source and drain shorted together. The variable

capacitance is achieved by controlling the gate to

diffusion/N-well potential within the range from –0.7 V

to 1.0 V, which drives the device from the depletion to

the accumulation. The capacitance per unit area can be

varied from Cmax (5.8 fF/µm2) to the value of 40% of Cmax

over this range. There is also a slight dependence on the

channel width and length. At the gate to source-drain

voltage (Vg-sd) below –0.7 V and above 1.0 V, a

depletion region in the gate polysilicon layer starts to

grow, leading to a reduction in the capacitance. The

device is found to be robust for Vg-sd from –1 V to +1

V. The Cmax/Cmin ratio is about 2, but Q value is more

than 45.

4. Simulation and result discussion

4.1. Design and implementation of a VCO with low

phase noise oscillating above 51 GHz.

The LC oscillator’s schematic is given in Fig. 1(a).

The microstrip line inductor and the MosVaractor are

used in the tank configuration. A pair of coupled nMOS

transistors (Mn1 and Mn2) and a pair of coupled pMOS

transistors (Mp1 and Mp2) are used in the positive

feedback to provide a negative resistance. The other

nMOS pair (Mn4 and Mn5) with two 50 resistors (R1 and

R2) forms the buffer. The bipolar tail transistor is used to

improve the phase noise and to supply a constant current

into the tank for the stable oscillation.

The capacitance of the tank (Ctank) at one of the output

node is expressed by the following equation [14]:

gdp2

dbpgspgdn2

dbngsnvartankCCCCCCCC (2)

Where, Cvar is the capacitance of a MosVaractor. The

capacitance value 23 fF with the Q value of 50 can be

obtained from the capacitance extraction of the

MosVaractor at the operation frequency of 55 GHz in

Fig. 4 Cgsn, Cdbn, Cgdn, Cgsp, Cdbp, Cgdp are the well-known

parasitic capacitances associated to the devices, the

overall capacitance is calculated as Ctank =330.8 fF. The

inductance per tank, L=50.6/2=25.3 pH with Q=38, was

Fig. 2. The comparison of inductance and Q between

transmission line and spiral inductor at 50 GHz

Fig. 3. The capacitance and Q versus Vg-sd for

MosVaractor at the operation frequency of 50 GHz.

Proceedings of The 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications ISBN 0-7695-1929-6/03 $17.00 © 2003 IEEE

![Page 4: [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications - Calgary, Alta., Canada (30 June-2 July 2003)] The 3rd IEEE International Workshop on](https://reader035.fdocuments.pl/reader035/viewer/2022080422/5750a5461a28abcf0cb0bde5/html5/thumbnails/4.jpg)

determined from Fig. 2 at the operation frequency 55

GHz. The oscillator frequency, f0 = 55.04 GHz is

achieved for Vcont=2.4 V. To verify the calculated

frequency, the VCO is simulated using Cadence

SpectreRF Simulator for pre-layout schematic see Fig.

1(a) at the same controlled voltage, the simulation result

is 55.08 GHz, which is in good agreement with the

theoretical calculation.

The active device speed is also another concern for the

high frequency operation. The single device gain cut-off

frequency, T, may sometimes be misleading. Expressed

by the formula,)( gdgs

m

TCC

g, can be doubled for a

differential transistor structure [15]. The fully

complementary cross-coupled VCO topology is a

differential structure where the gate-source and gate-drain

capacitors that are viewed by each transistor, Cgs + Cgd,

are reduced to be half that of a single transistor. Hence,

even though the cutoff frequency of the nMOS transistor

is 45 GHz for the IBM BiCMOS-6HP technology [8], it is

still possible to design an LC VCO that can operate above

51 GHz.

A 51.8 GHz complementary cross-coupled LC VCO is

designed and simulated using the IBM BiCMOS-6HP

process. The power consumption of the VCO core is 9

mW and the total power consumption including the buffer

is about 25 mW. The VCO can be tuned from 50.77 GHz

to 51.8 GHz with the tuning range 0.93 GHz, and the

phase noise is about –89.5 dBc/Hz at 100 kHz offset

frequency and –106 dBc/Hz at 600 kHz offset frequency

from post-layout simulation respectively as shown in Fig.

4 and Fig. 5. To the best of authors’ knowledge, this is

the highest oscillation frequency for a fully integrated

VCO, which is designed using a commercial BiCMOS

technology.

4.2. The parasitic extraction and analysis

The parasitic components due to the interconnect

metals and the devices in the layout affect the operation

of the practical circuit, usually degrading the

performance. Parasitic coupling is inevitable, but it can be

minimized by a carefully layout drawing. The parasitic

capacitances and resistances are extracted and the

schematic is modified accordingly using special

components, RCnet, to represent the extracted parasitics

as presented in Fig. 6. The effects of these parasitic RCnet

components on the VCO performance are investigated.

There are two sets of critical nodes that have high

parasitic effect: the connection of the output buffer

transistor’s gate and the VCO core (the cross-coupled

nMOS transistor’s drain terminal), i.e. RCnet1 and

RCnet2. These parasitics shift the operation frequency.

The second critical connection is the one between the 50

resistor and the drain of buffer transistor, i.e. RCnet3

and RCnet4 . The amplitude of the output voltage is

Fig. 4. The tuning characteristics of the VCO.

Fig. 5. The phase noise performance of the VCO

Fig. 6. The schematic of the VCO with added

parasitic components

Proceedings of The 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications ISBN 0-7695-1929-6/03 $17.00 © 2003 IEEE

![Page 5: [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications - Calgary, Alta., Canada (30 June-2 July 2003)] The 3rd IEEE International Workshop on](https://reader035.fdocuments.pl/reader035/viewer/2022080422/5750a5461a28abcf0cb0bde5/html5/thumbnails/5.jpg)

reduced due to the parasitic resistances at this point. The

layout is optimized as much as possible to obtain the

minimum parasitic components at the nodes.

The maximum oscillation frequency is lowed by 5

GHz, and the phase noise is increased by 5 dB/Hz at 600

kHz frequency offset when the parasitic capacitance is

increased from 10 fF to 90 fF at the RCnet1 and RCnet2.

The frequency tuning range also suffers slightly from the

parasitics, and it is reduced by 150 MHz.

Based on above consideration, the optimized layout of the

LC VCO is presented in Fig. 7. The parasitic components

“RCnet” are extracted and the post-layout simulation are

done for our design. The comparisons between the pre-

layout and the post-layout simulation are demonstrated in

Fig. 4 and Fig. 5. The maximum oscillation frequency is

shifted down 3.28 GHz (from 55.1 GHz to 51.8 GHz), the

phase noise is degraded by 2.5 dB/Hz at 100 kHz offset

frequency (from 92 dBc/Hz to 89.5 dBc/Hz at 100 kHz

offset frequency). Thus, a 51.8 GHz LC VCO with low

phase noise is achieved by using IBM BiCMOS-6HP

technology, the performance is summarized in Table.1.

5. Conclusion

A low power and low phase noise VCO with

oscillation frequencies around 51.8 GHz with low phase

noise of –106dBc at the 600kHz offset frequency and a

frequency tuning range of 0.93 GHz is achieved using

the commercial IBM BiCMOS-6HP technology. The

operation of the fully complementary cross-coupled LC

VCO using Bipolar-T is analyzed and the parasitic

components in the layout are detailed. A simple

optimization method for the complementary LC VCO

layout is also employed in the design. Fully integrated

above 50GHz VCOs are the crucial blocks in SONET

systems operating at speeds higher than 40 Gb/s and in

the application of satellite communication operating at V-

band.

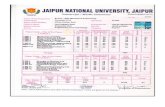

Table 1. Summary of VCO performances

Complementary Cross-

Coupled VCO Design

Pre-layout Post-layout

Maximum Frequency 55.08 GHz 51.8 GHz

Phase Noise @ 100KHz -92 dBc/Hz -89.5

dBc/Hz

Tuning Range* 1.1 GHz 0.93 GHz

Tuning % 2.0 1.8

Max. Output (core) 1.6 Vp-p 1.2 Vp-p

Max. Output (Buffer) 0.55 Vp-p 0.4 Vp-p

Total Bias Current 12.5 mA

Supply Voltage 2.0 V

Power Consumption

without buffer 9 mW

Power Consumption with

buffer 25 mW

Chip Area without buffer 120 x 152 m2

Chip Area with buffer 600 x 610 m2

6. References

[1]. Y. Kwon, “Large signal analysis and experimental

characteristics of monolithic InP-based W-band HEMT

oscillator,” in 21th European Microwave Conf. Tech Dig.,

Stuttgart, Germany, Sept. 1991, pp.99-101.

[2]. H. Wang, “Monolithic W-band VCO’s using

pseudomorphic AlGaAs/InGaAs/GaAs HEMT’s,” in 14th Ann.

IEEE GaAs IC Symmp. Dig., Miami, FL. Oct.1992, pp.47-50.

[3]. H. Wang, “A 50GHz VCO in 0.25 m CMOS,” in IEEE

Solid State Circuits Conference Digest of Technical Papers,

Feb. 2001, pp.372-373.

[4]. K. Riepe, “35-40 GHz Monolithic VCO’s utilizing high

speed GaInP/GaAs HBT’s,” in IEEE Microwave and Guide

Wave Letters. vol.4, no.8, Aug. 1994, pp274-276.

[5]. S. Yamahata, “ Ultra-high fmax and fT InP/InGaAs double-

hetrojunction bipolar transistors with step-graded InGaAsP

collector,” in 16th Annual IEEE GaAs IC Sump. Dig.,

Philadelphia. PA, Oct.1994, pp.245-348.

[6]. K. W. Kobayashi, “InP based HBT millimeter-wave

technology and circuit performance to 40GHz,” in IEEE 1993

Microwave and Millimeter-wave Monothic Circuit Symp. Dig.,

Atlanta. GA, June 1993, pp.85-88.

[7]. Ali Hajimiri, “A General Theory of Phase Noise in

Electronical Oscillators,” in IEEE journal of solid-state circuits,

vol.33, No.2 Feb. 1998.

[8]. IBM BiCMOS-6HP Model Reference Guide, pp.3-144.

Fig. 7. The layout for 51.8GHz

Proceedings of The 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications ISBN 0-7695-1929-6/03 $17.00 © 2003 IEEE

![Page 6: [IEEE Comput. Soc 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications - Calgary, Alta., Canada (30 June-2 July 2003)] The 3rd IEEE International Workshop on](https://reader035.fdocuments.pl/reader035/viewer/2022080422/5750a5461a28abcf0cb0bde5/html5/thumbnails/6.jpg)

[9]. L.Dauphinee,M. Copeland, and P. Schvan, “A balanced

1.5GHz Voltage Controlled oscillator with an integrated LC

resonator,” in Solid State Circuits Conference Digest of

Technical Papers, Feb.1997, pp.390-391.

[10]. J. Craninckx and M.Steyaert, “ A 1.8GHz low phase noise

CMOS VCO using optimized hollow spiral inductors,” in IEEE

J. Solid-State Circuits, vol.32, no.6, May 1997, pp.736-744.

[11]. J. Craninckx, M.Steyaert, and H. Miyakawa, “A fully

integrated spiral LC CMOS VCO set with prescalar for GSM

and DCS-1800 systems, ” in Proc. CICC, May 1997, pp.403-

406.

[12]. T. H.Lee, “OSCILLATOR PHASE NOISE: A

TUTORIAL (Invited),” in IEEE 1999 custom integrated

circuits conference.

[13]. Y. Tsividis . “ Operation and Modeling of The MOS

Transistor,” Second edition, Mcgraw-hill international editions,

Electronical engineering Series, pp.201-202.

[14]. D. Ham, “ Concept and Methods in Optimization of

Integrated LC VCO,” in IEEE journal of solid-state circuits,

vol.36, no.6, Jun. 2001, pp.896-907.

[15]. Jan Craninckx, “Low-Noise Voltage-Controlled Oscillator

Using Enhanced LC-Tanks, ” in IEEE transactions on circuit

and systems – II: analog and digital signal processing, vol.42,

No.12, Dec. 1995.

Proceedings of The 3rd IEEE International Workshop on System-on-Chip for Real-Time Applications ISBN 0-7695-1929-6/03 $17.00 © 2003 IEEE