32ビットのCPUコアIPをはじめAndes Technology NEW PRODUCT INFO|...

Transcript of 32ビットのCPUコアIPをはじめAndes Technology NEW PRODUCT INFO|...

APS MAGAZINE 4342 APS MAGAZINEVolume.11 2015.8 4342 Volume.11 2015.8

世界で5本の指に入る組込みシステム向け32ビットコアIP

台湾のアンデスは、2005年創業の半導体IP

ベンダーである。「AndesCoreは、世界で5本

の指に入る組込みシステム向け32ビットコアIP

です。AndesCoreを搭載したカスタムチップを

中心に、システム開発のためのトータルソリュー

ションを提供しています」(Frankwell氏)という。

彼らが標榜するトータルソリューションとは、

CPUコアとしてAndesCore、各種ペリフェラル

IP、AndesCoreのベースとなる命令セットアー

キテクチャAndeStar™、SoC開発プラットフォー

ムのAndeShape™といったカスタムチップを開

発するためのツールがある。さらに、Eclipse

ベースの統合開発環境のAndeSight™、各種

ソフトウェア群のAndeSoft™など、完成したカ

スタムチップ上でソフトウェアを開発するための

ツールが用意されている。

「2008年からライセンスの提供を開始してお

り、すでにAndesCoreをご採用いただいた企

業は100社を超え、チップ数は数億個にのぼり

ます」(Al氏)。国別の売上げは、2014年実績

で台湾65%、中国12%、日本8%、韓国6%、

欧米9%である。

AndeStarは、32ビットRISCスタイルの命令

セットアーキテクチャ(ISA)である。命令長とし

て16ビットと32ビットが混在しており、コード

効率と速度の最適化が図れる。

AndesCoreは、32ビットRISCスタイルのCPU

コアであり、RTL(Register Transfer Level)

記述のソフトコアだ。N、D、E、Sというシリー

ズに展開されており、「N」は高性能な汎用タイ

プであり実装時のサイズが小さくできる。「D」は

SIMD命令を持つDSPコアであり、「E」は特定

のアプリケーション向けに命令セットを拡張でき

る。「S」はセキュリティが強化されたコアとなる。

性能や機能の異なる複数のAndesCoreをラインアップ

AndesCoreの製品として現在、「AndesCore

N7、 N8、 E8、S8、N9、 N10、D10、 N12、

N13を中心としたファミリがラインアップされて

いる(図1)。

AndesCore N7ファミリは2ス テ ー ジ の

パイプラインを搭載し、8ビットマイコンからの

アップグレードに向く。実際の製品として最大

現在、CPUコアのIPとしてARM®(Cortex®シリーズなど)が主流となっているが、他にもさまざまなIPベンダーが存在する。2005年に台湾

で創業されたAndes Technology社(以下、アンデス)もそのひとつで、32ビットRISCタイプのCPUコアIPであるAndesCore™ファミリを

ラインアップしている。ここではARMとの比較も含めて、アンデスのCPUコアをはじめとする組込みシステム開発のための、トータルソリュー

ションについて聞いた。

500MHz動作の「N705」がある。

AndesCore N8ファミリは、3ステージのパ

イプラインを搭載し16/32ビットコアからのアッ

プグレードに向けたもので、製品として「N801」

が用意されている。「AndesCore N7・ N8ファ

ミ リ は、ARMのCortex-M0/M0+/ARM7な

どに相当します。ゲート数が小さく電力効率が

高いという特長を持ち、コンシューマアプリケー

ションで8ビットや16ビットマイコンを置き換え

るものとなるでしょう」(Charlie氏)。

さらに、命令セットを拡張できるAndesCore

E8ファミリの「E801」、セキュリティを強化した

AndesCore S8ファミリの「S801」もある。「E8

ファミリはIoTアプリケーションがターゲットと

なります。独自のアンデスカスタム拡張(ACE)

は、IoTアプリケーションのためのコアとして最

適です。S8ファミリは、スマートカードや安全性

を高めたカードアプリケーションに向いています」

(Charlie氏)。

ミッドレンジに相当するのが、AndesCore

N9とAndesCore N10ファミリだ。N9ファミリ

の「N968A」は5ステージのパイプラインを搭載

している。ARMに置き換えるとCortex-M3や

ARM9に相当する。N10ファミリの「N1068A」

も5ステージのパイプラインの他に、FPUを搭

載しており、ARMのCortex-M4やARM9に相

当し、より高い性能を有する。

さらにDSP機 能 を 強 化 さ せ たAndesCore

D10ファミリは、強力なSIMD命令により、MP3

デコードなど画像や音声処理での高速処理を実

現する。

「AndesCore N9ファミリは、高い性能を持

つ汎用マイコンを構成でき、自動車の各種制御

やストレージなどの組込みコントローラなどに向

いています。N10ファミリは、メディアプレーヤ

やスマートグラス、ウェアラブル、モータ制御、

電力管理など幅広いアプリケーションでのニー

ズにお応えします」(Charlie氏)。

そしてハ イエンドとなる の がAndesCore

N13ファミリであり、8ステージのパイプライン

を有する。製品となる「N1337」は最大1.5GHz

で動作する。ホームエンターテインメント、デジ

タルセットトップボックス、ネットワーキング、モ

バイルインターネットデバイスなど、高い性能が

必要となるマルチメディア処理に向けたものだ。

さまざまなクラスにおける比較でARMコアに勝っている

AndesCoreとCortexのそれぞれ標準ライブ

ラリを用いた電力効率(DMIPS/MHz)を調べ

た 結 果、N7とCortex-M0+で は142%、E8

とCortex-M0で は145%、N9とCortex-M3

で は151%、N10とCortex-M4で は130%、

N13とCortex-A5で は177% と、 い ず れ も

AndesCoreが 性 能 面で勝っている(2015年

7月 アンデス社調べ)。「電力効率や面積効率

(性能/面積)が良くなるようにコアを開発し

ていおり、極めて競争力のあるPPA(Power,

Performance and Area)を実現しています」

(Charlie氏)。

AndesCoreは自由に組み合わせたマルチ

コア化も可能だ。「ある日本の大手通信事業者

様 は、N13を3個、N10を5個 で 合 計8個 の

AndesCoreを搭載した通信用チップを開発し

ました」(Frankwell氏)。

CPU周りに必要なペリフェラルIPも用意して

いる。フラッシュメモリ専用のキャッシュメモリで

あるFlashFetch IPを含むバスマトリックス、バ

スブリッジ、DMAコントローラ、GPIO、I2C、

各種タイマ、SPI、UARTなどをカバーしている。

IPに対するライセンス料が複雑なベンダーも

あるが、アンデスは極めてシンプルな形態となっ

ている。「IPのライセンス形態は極めてシンプル

であり、オプションで無制限にすることもできま

す。ライセンスは年契約であり、特に大口のお

客様にはメンバーシッププログラムを用意して

おり、ペリフェラルも含めたすべてのIPを自由

に使用できます」(Al氏)という。すべてのIPは

RTLコードで提供されている。

特定のアプリケーションに向けた半導体チップ

を開発する場合、しばしば比較されるのがASIC

とFPGAだ。Charlie氏 も「ASICと 比 較 し た

FPGAのメリットは、柔軟性と市場投入までの時

間の短さです。 技術的な要件(性能、消費電力、

面積)を満たしているのであれば、少ない数量

でも短納期で製品化したいのでればFPGAにメ

リットがあります。AndesCoresやコンパニオ

ンIPは、すべてASICとFGPAに使用することが

できます」という。すなわち、アンデスのコアIP

を用いればASICかFPGAかの選択に悩むこと

なく、それぞれのメリットが活かせる。「弊社は

IPベンダーですが、パートナーとしていくつかの

大手ASIC設計サービス会社があり、お客様に

集合写真(左より)

Andes Technology CorporationVice PresidentSales DivisionAl Lin 氏

Chief Technical OfficerSenior VPCorporate OfficeCharlie Su 氏

PresidentFrankwell Lin 氏

Andes Technology | NEW PRODUCT INFO

図1:CPUコアであるAndesCoreのラインアップ。

消費電力

性能

Panther

N13:

N1337> 1 . 5 G H z

Advanced

(8 stages)

N1068> 1 G H zN968A

> 1 G H z

Mid-range

N801> 8 3 0 M H z

Deeply Embedded16b/32b app.

N705> 5 0 0 M H z

N10:5 stages, Caches,

MPU/MMU,FPU, BrPred

N9:5 stages,LM, AXIN8:

3 stagesN7:

Cortex®-M0/M0+/ARM7 M3/ARM9 M4/ARM9 ARM11/R4/A5/A7

*Frequency@TSMC28HPM:Lvt library, 125˚C, slow silicon, 0.9Vdd

2 stages

Upgrade for8b MCU

E801Extensible

S801Secure Core

D10DSP SIMD

32ビットのCPUコアIPをはじめシステム開発のためのトータルソリューションを提供

APS MAGAZINE 4544 APS MAGAZINEVolume.11 2015.8 4544 Volume.11 2015.8

最適なソリューションを提供できます」(Charlie

氏)という。

無償貸与のBSPを用意するなどソフトウェア開発環境も充実

「ソフトウェア開発環境としてAndeSightを提

供しています。これはEclipseベースの統合開

発環境であり、多くのプラグインが用意されて

い ます」(Charlie氏)。GNUコン パ イラ も 用

意されており、性能とコードサイズが最適化さ

れたコードを生成できる。GNUデバッガや独

自のデバッガも用意されている。さらには、解

析ツールも充実しており、関数のプロファイリ

ング、コードカバレッジ、リアルタイムOSの状

態ビューなど、さまざまなソフトウェアの動き

をビジュアルで解析可能だ。新しい命令のI/O

を 定 義 後、COPILOT(Custom-OPtimized

Instruction deveLOpment Tools)ツ ー ル

を用いることで、コンパイラやデバッガ、シミュ

レータなどの関連ツールのためのコンポーネン

トやRTLコードを生成できる。

エコシステムも充実している。ローターバッ

ハ 社 のTRACE32/ JTAGデ バ ッ ガ やSoC向

けにカスタマイズされた統合開発環境である

CooCox、OSとしてはµITRONで高いシェアを

誇るイーフォース社のµC3をはじめ、Linuxや

µBoot、Contiki、eCos、Thread-X、µC/

OS-II and III、Nucleusがあげられる。ミドル

ウェアとしてはZigBeeやBluetooth、ファイル

システム、USB、セキュリティスタックなど、多

くのミドルウェアが提供されている。

もちろ ん 評 価 ボ ードと評 価 ボ ード 用BSP

(Board Support Package)も準備されてい

る(図2)。「すべてのAndesCoreライセンシー

のためにBSPを無料で貸し出しています。多く

のサンプルコードも用意され、効率的な開発を

支援します」(Charlie氏)。このBSPは9カ月ご

とにアップデートされ、常に最新のものを使用

できるという。「技術サポート部隊は、お客様に

実際にお会いしてのミーティングに加え、Web

会議や電話、電子メール、Eサービスなど、さ

まざま手段で手厚いサポートを提供しています。

Eサービスは、お客様の質問などに対して、で

きるだけ早くフィードバックするもので、基本

的に24時間対応となっています」(Frankwell

氏)。日本では、経験豊富なトリトン株式会社が

総代理店としてサポートしているので安心だ。

今後は既存の分野に加えIoT市場に注力していく

アンデスの製品は、すでにタッチパネルやワ

イヤレス、コントローラといった携帯電話の周辺

機能、マイコン、IoT、ハイエンドネットワーク、

マルチメディア、FAのコントローラ、センサシ

ステムなど幅広い市場で採用されている。

これから市場規模の拡大が期待されるのが

IoT分野だ。「今後10年で500億個もの機器間

通信が実現されると見ています。弊社ではIoT

のためのソリューションを備えており、すでに

ワールドワイドで20社以上のお客様をサポート

しています」(Al氏)。

来たるIoT時代を見据えて、セットメーカーに

向けたWebサイト「www.knect.me」を開設

している。www.knect.meによって、チップ

ベンダー、サードパーティ、アプリケーション開

発者、システムベンダーという4つが関連し合っ

たIoTソリューションの実現をサポートする。さ

らに、Knect SoCプラットフォーム、Knectソ

フトウェアスタック、Knectアプリケーションプ

ラットフォーム、Knect開発ツールといったIoT

ソリューションを用意している。

Charlie氏は、「多くの優れた製品や産業が

日本企業によってもたらされたことからも分か

るように、日本のメーカーは極めて革新的です。

SoCとアプリケーションがますます複雑になって

きた今日、アンデスは日本メーカーの技術革新

を継続し、さらにアンデスのプロセッサソリュー

ションとソフトウェアを活用いただくことで、お

客様の製品差別化を支援していきます」という。

「今年の10月14日に新横浜国際ホテルで技術

セミナーを開催しますので、ぜひご来場いただ

きアンデスの性能を体感いただきたい」(Al氏)。

今 後 も 超 低 消 費 電 力 か つ 高 性 能 なIPを

提 供することに 注 力していくという。 最 後 に

Frankwell氏は、「プラットフォームIP、コンパ

ニオンIP、組込みプロセッサを開発するための

ソフトウェアとハードウェアの開発、デバッグ、

ツールチェーン、BSP、ならびに各種アプリケー

ションのためのエコシステムを提供していくこと

に加えて、より上位のプロセッサIP、高度な命

令セットアーキテクチャ、より深いステージのパ

イプライン、超低消費電力、より多くのスレッド

などを開発することで、お客様のシステムの競

争力確保に貢献していきます」とまとめた。

図2:ザイリンクスのVirtex®-5を搭載した評価ボード。このボードが無償で借りられる。

Andes Technology | NEW PRODUCT INFO

ARMの対抗馬は存在する。MIPSでもARCでもない。それがAndes

コアだ。CPU性能はもちろん、豊富なツール群やBSP、エコシステム、

サポート体制など充実してきている。テクノロジーだけの勝負ではない

ところも分かっているのがAndesの本当の強みかもしれない。

Technical NOTE

主な利点

性能

■非常にコンパクトなプログラムサイズ

■ほとんどの32ビット動作は1サイクル実行

■大規模な分岐予測による高速な分岐制御

■高速メモリアクセス

拡張性

■C言語による組込みプログラミング

■JTAGデバッグ、パフォーマンス監視機能

■バイエンディアンでのデータアクセス

電力管理

■クロックおよび論理回路のゲーティング

■スタンバイ命令による電力管理

■コア対バスのクロック比はN対1

無料セミナー情報(定員80名)

日時:2015年10月14日(水) 13:30〜

場所:新横浜国際ホテル

お問い合せ:[email protected]

■SW電源管理のための待機命令

■16入力までの割り込みコントローラ内蔵

■3階層のHWレベルのネスト割り込み

■オプションによる統一または

外部のローカルメモリインタフェース

■ユーザおよびスーパーユーザの

両モードをサポート

■メモリマップドI/O

■コプロセッサインタフェース

メモリ管理・保護機能

■TLB(Translation Lookaside Buffer)

■オプションによる

ハードウェアページテーブルウォーカー

■2グループのページサイズをサポート

■8個の領域のメモリを保護

メモリサブシステム

■命令&データキャッシュ

■命令&データローカルメモリ(ILM/DLM)

バスインタフェース

■同期/非同期AHBバス:1または2ポート

■同期AXIバス:0、1または2ポート

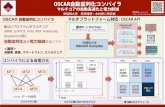

高性能AndesCore™N13ファミリは、ホーム

エンターテインメント、デジタルセットトップボッ

クス、ネットワーキング、モバイルインターネッ

トデバイスなどの市場のパフォーマンス要件に

対応するように設計されています。メモリ管理ユ

ニットと8段のパイプラインを実装し、1GHz以

上のクロックで動作し、2.05DMIPS/MHzとい

うパフォーマンスを提供します。

主な特徴

CPUコア

■2.05D MIPS/MHz, 3.13CoreMark/MHz

■AndeStar™V3アーキテクチャ

■8段パイプライン

■16/32ビット混在可能な命令フォーマット

■32個の汎用32ビットレジスタ

■シャドウのスタックポインタ

■動的分岐予測(32/64/128/256 BTB)

■積和および積差命令

■整列・非整列の複数ワードのロード/ストア

COP COP I/F

JTAG JTAG/EDM

Power mgmt & IRQ

1or 2AXI

1or 2AHB

Standby&VIC

DTLB

ITLB

N13 µCore MMUMPU DMA

External Bus Interface

DataCache

DataLM

Instr.LM

Instr.Cache

SoC向け 32-bit プロセッサAndesCore™ N13 family

日本代理店:トリトン株式会社TEL:080-4002-0768E-mail:[email protected]

「Debug "hello world" on ADP-XC5 FPGA board」http://go.aps-web.jp/11-andes

QRコードアプリで関連デモ動画を再生できます。

AndesCore™ N13 family : Functional Blocks

Andes Technology

http://www.andestech.com/